# **User Manual**

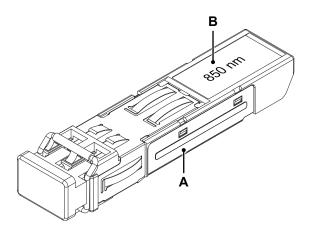

English

Desktop and Rack Mount Tethered Data Acquisition System

Document version 3.0 - July 2020

References made to the Perception software are for version 7.40 or higher

For HBK's Terms and Conditions visit www.hbm.com/terms

Hottinger Brüel & Kjaer GmbH Im Tiefen See 45 64293 Darmstadt Germany Tel: +49 6151 80 30 Fax: +49 6151 8039100

Email: info@hbm.com www.hbm.com/highspeed

Copyright © 2020

All rights reserved. No part of the contents of this document may be reproduced or transmitted in any form or by any means without the written permission of the publisher.

## LICENSE AGREEMENT and WARRANTY

For information about LICENSE AGREEMENT AND WARRANTY refer to www.hbm.com/terms.

## **Trademarks and patents**

StatStream<sup>®</sup> is a registered trademark of HBK in the European Union and a trademark in other countries.

StatStream® is patented in the US, Patent No. 7,868,886; patent pending in other countries.

## Legal statement

This product uses GNU General Public Licensed (GPL) software, the source code is available at:

www.hbm.com/highspeed

For more information please refer to the following website: <a href="https://www.gnu.org">www.gnu.org</a>

This product includes software developed by the OpenSSL Project for use in the OpenSSL Toolkit.

www.openssl.org/

A04377\_03\_E00\_00 HBK: UNRESTRICTED

| Table of | of Contents                                                | Page |  |

|----------|------------------------------------------------------------|------|--|

| 1        | About this manual                                          | 16   |  |

| 1.1      | Symbols used in this manual                                | 16   |  |

| 1.2      | Manual conventions                                         | 17   |  |

| 2        | Safety Messages                                            | 18   |  |

| 2.1      | Introduction                                               | 18   |  |

| 2.2      | Grounding                                                  | 21   |  |

| 2.2.1    | Mains power cord                                           | 22   |  |

| 2.3      | Instrument symbols                                         | 23   |  |

| 2.4      | Protection and isolation                                   | 24   |  |

| 2.4.1    | Measurement categories                                     | 24   |  |

| 2.4.1.1  | Categories in accordance with IEC 61010-2-030:2010         | 24   |  |

| 2.4.2    | Basic insulation versus reinforced                         | 26   |  |

| 2.4.2.1  | Additional means of protection for single fault conditions | 27   |  |

| 2.4.3    | Protection                                                 | 28   |  |

| 2.4.4    | Overvoltage/current protection                             | 28   |  |

| 2.4.5    | Isolation                                                  | 29   |  |

| 2.5      | Environment                                                | 30   |  |

| 2.6      | Laser Safety                                               | 31   |  |

| 2.7      | Manual handling of loads                                   | 32   |  |

| 2.8      | International safety warnings                              | 33   |  |

| 2.9      | Operation of electrical installations                      | 49   |  |

| 3        | Normative Documents and Declarations                       | 50   |  |

| 3.1      | Electrical                                                 | 50   |  |

| 3.1.1    | Electrostatic Discharge (ESD)                              | 50   |  |

| 3.1.2    | Electromagnetic Compatibility (EMC)                        | 51   |  |

| 3.2      | Environment                                                | 53   |  |

| 3.2.1    | RoHS and WEEE - Waste Electrical and Electronic Equipment  | 53   |  |

| 3.2.1.1  | Packaging                                                  | 53   |  |

| 3.2.2    | China RoHS                                                 | 53   |  |

| 3.3      | CE Declaration of conformity                               | 55   |  |

| 3.4      | FCC Class A Notice                                         | 56   |  |

| 4        | Batteries                                                  | 57   |  |

| 4.1      | General                                                    | 57   |  |

| 4.2      | Removal and replacement                                    | 58   |  |

| 4.3      | Recharging                                                 | 61   |  |

| 4.4   | Disposal                                       | 62 |

|-------|------------------------------------------------|----|

| 5     | Mains Power                                    | 63 |

| 5.1   | Power and frequency requirements               | 63 |

| 5.2   | Connecting power                               | 64 |

| 5.3   | Fuse requirements and protection               | 66 |

| 5.4   | Fuse replacement                               | 67 |

| 6     | Introduction                                   | 68 |

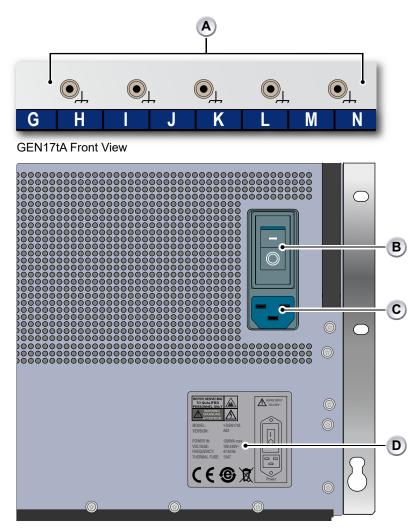

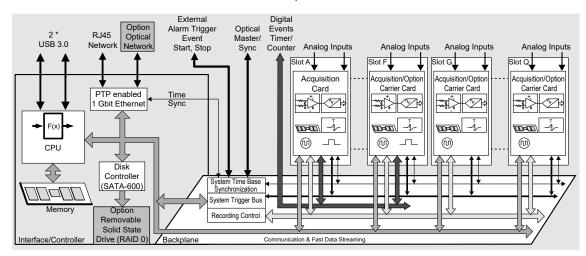

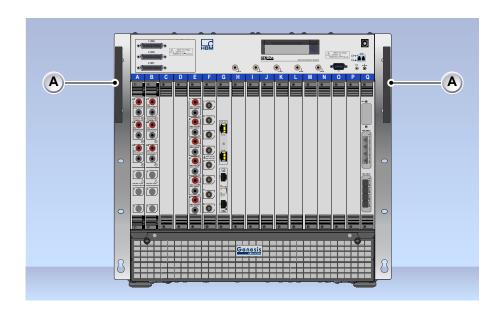

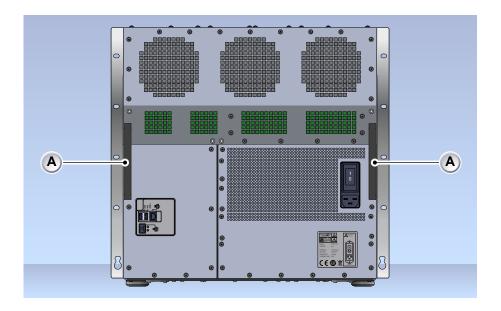

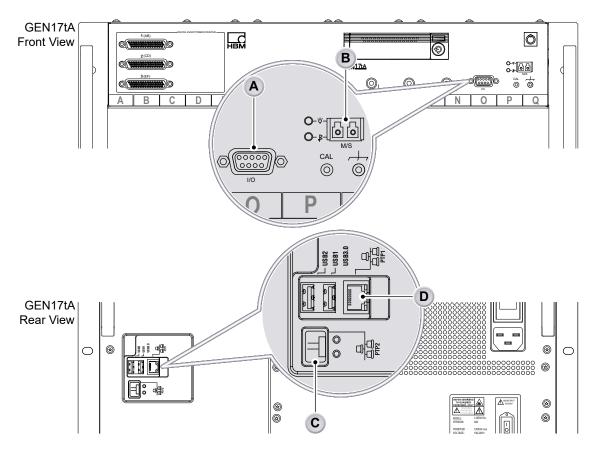

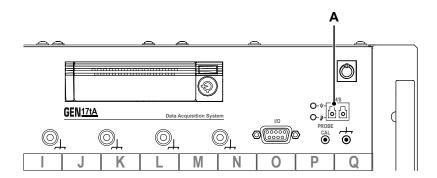

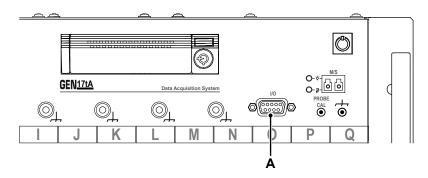

| 6.1   | Introducing GEN17tA                            | 68 |

| 6.2   | Mainframe overview                             | 69 |

| 6.2.1 | Mainframe feature comparison                   | 70 |

| 6.3   | Hardware                                       | 71 |

| 6.3.1 | PCI-e/CPCI backplane                           | 71 |

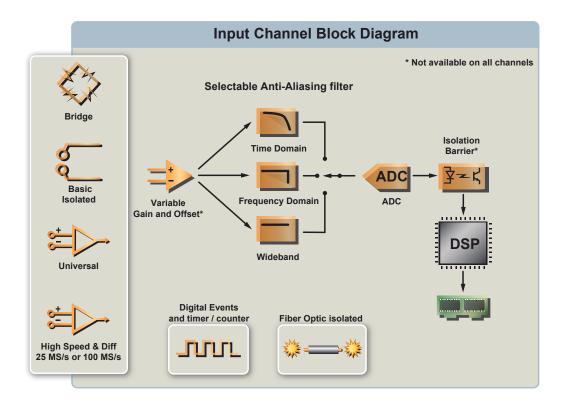

| 6.3.2 | Input cards                                    | 72 |

| 6.3.3 | Master/Sync support                            | 72 |

| 6.3.4 | Thermal protection                             | 72 |

| 6.4   | Acquisition                                    | 74 |

| 6.4.1 | StatStream®                                    | 74 |

| 6.5   | Signal conditioning                            | 76 |

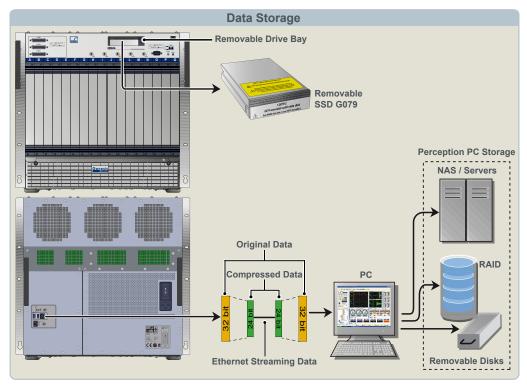

| 6.6   | Data storage                                   | 77 |

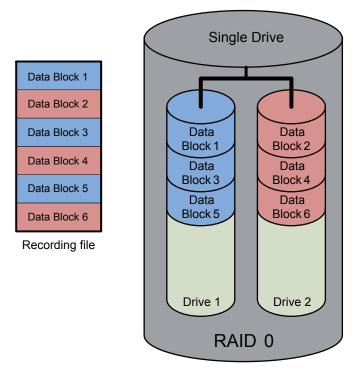

| 6.6.1 | RAID 0 technology                              | 78 |

| 6.6.2 | Solid State Drive (SSD) technology             | 80 |

| 6.7   | Interface/Controller section                   | 81 |

| 7     | Setting up the GEN17tA                         | 82 |

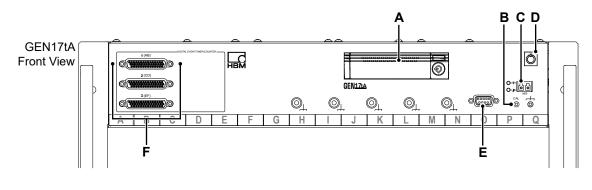

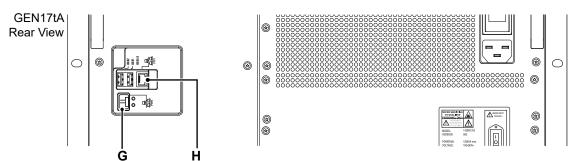

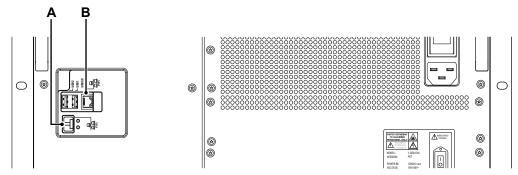

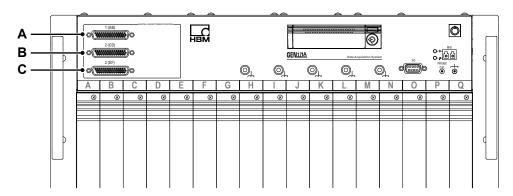

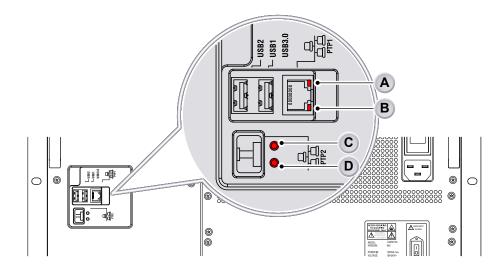

| 7.1   | GEN17tA connections                            | 82 |

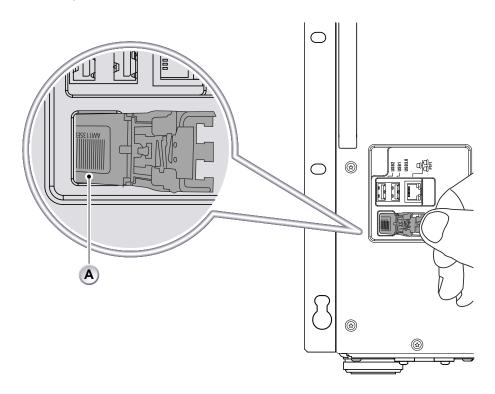

| 7.1.1 | Removable drive bay                            | 83 |

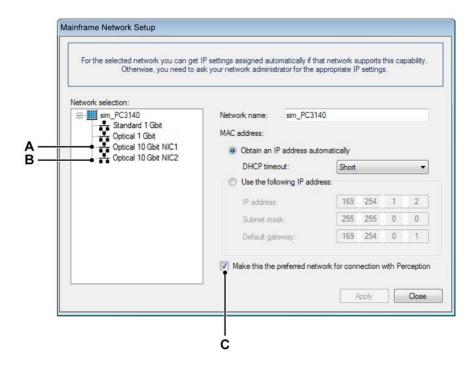

| 7.2   | Connecting the GEN series to a network         | 86 |

| 7.2.1 | Default network settings                       | 87 |

| 7.2.2 | Connecting the GEN series directly to a PC     | 87 |

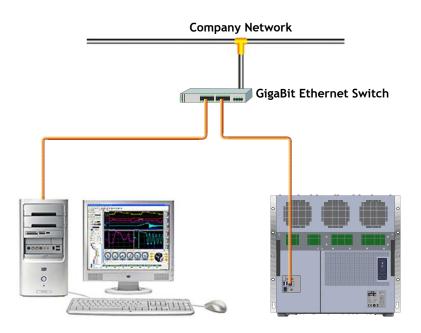

| 7.2.3 | Connecting the GEN series to a company network | 88 |

| 7.2.4 | Note on IP address and DHCP                    | 89 |

| 7.2.5 | Network testing and troubleshooting            | 90 |

| 7.3   | Restore default network settings               | 91 |

| 7.4   | Removing and installing input cards            | 92 |

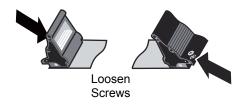

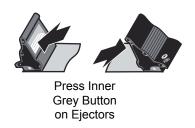

| 7.4.1 | Removing cards                                 | 92 |

| 7.4.2 | Installing cards                               | 93 |

| 7.5   | Handles                                        | 95 |

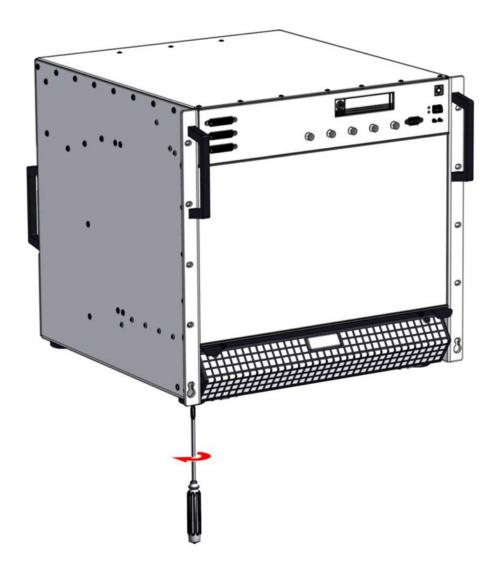

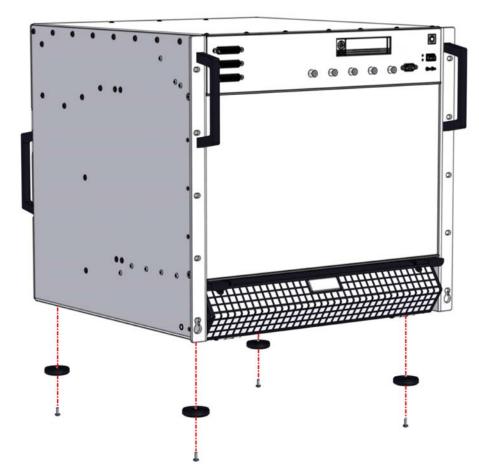

| 7.6   | Feet                                           | 96 |

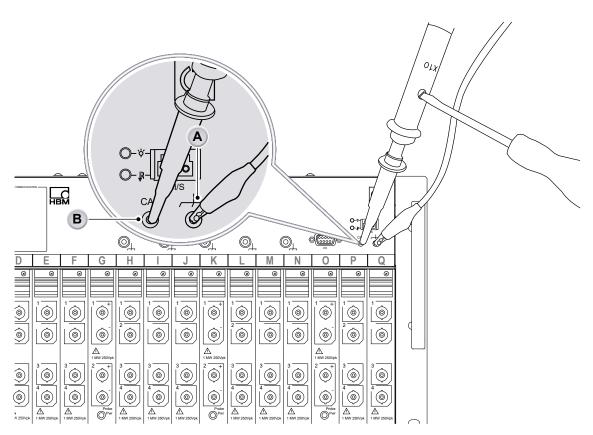

| 7.7    | Probe calibration                                         | 98  |

|--------|-----------------------------------------------------------|-----|

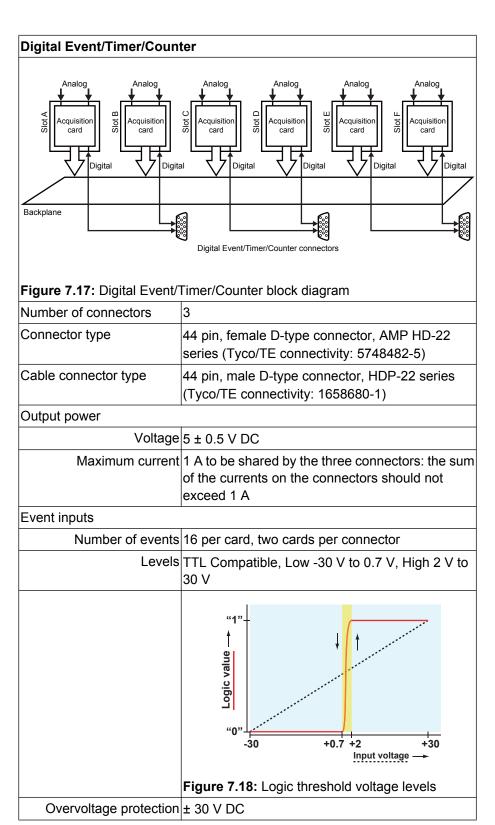

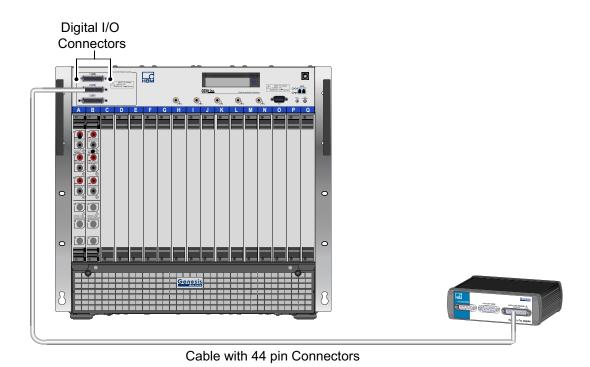

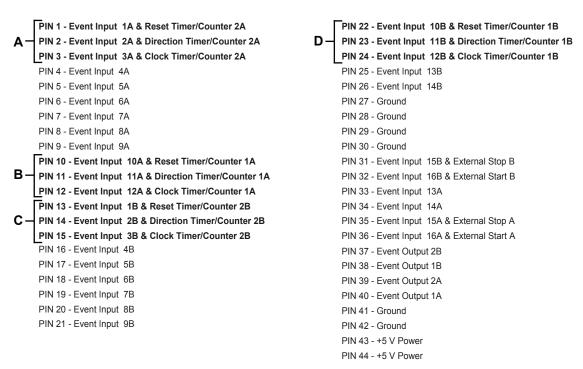

| 7.8    | Digital Event/Timer/Counter                               | 100 |

| 7.8.1  | Isolated event adapter                                    | 103 |

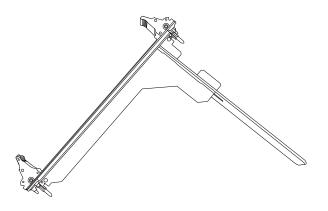

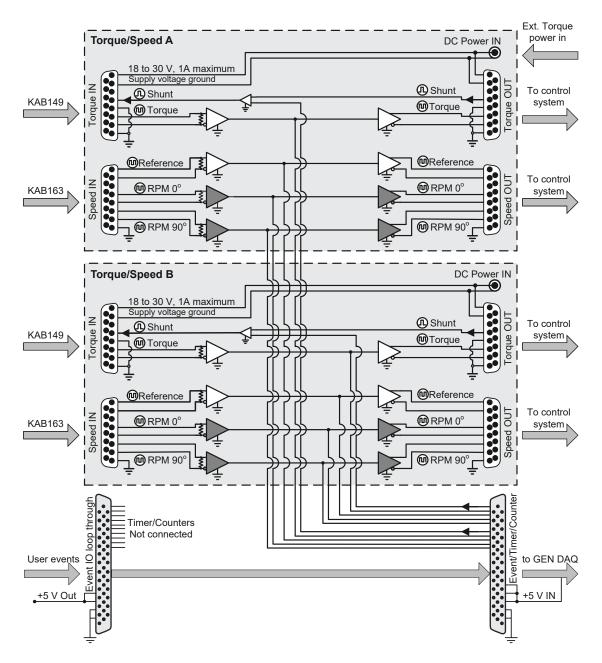

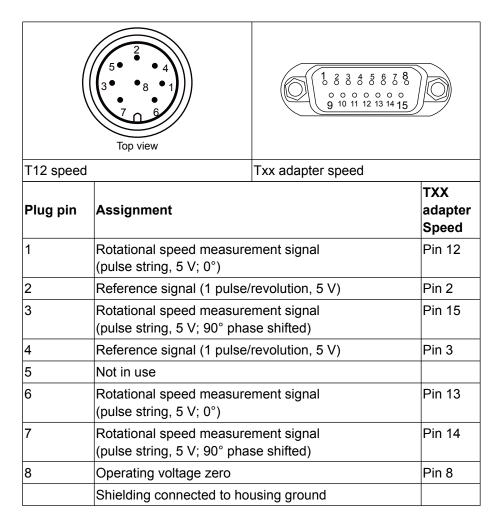

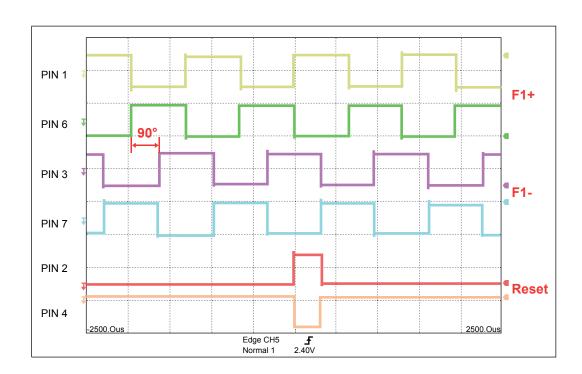

| 7.8.2  | Torque/RPM adapter                                        | 104 |

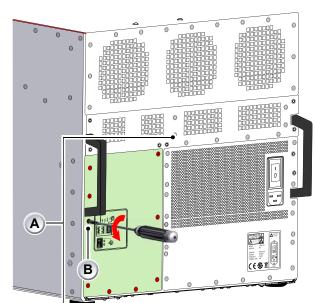

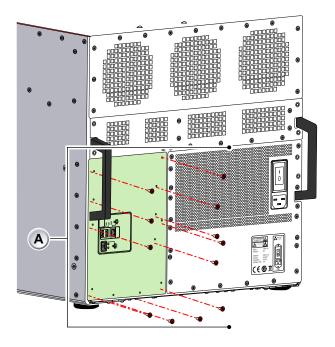

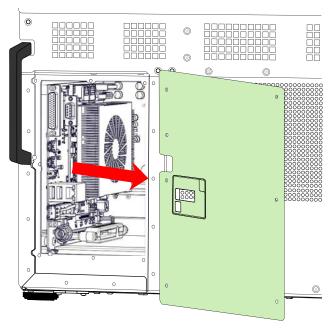

| 7.9    | Accessing the CPU section                                 | 107 |

| 7.10   | Air filter replacement                                    | 110 |

| 8      | Getting Started                                           | 114 |

| 8.1    | GEN17tA control                                           | 114 |

| 8.2    | Connecting GEN17tA to Perception                          | 116 |

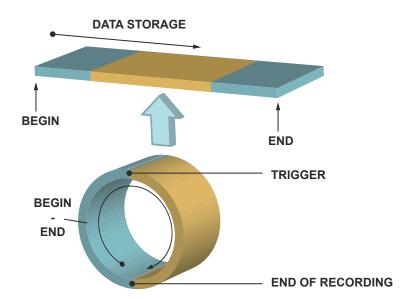

| 9      | Acquisition and Storage                                   | 121 |

| 9.1    | Introduction                                              | 121 |

| 9.2    | Recording                                                 | 122 |

| 9.3    | Storage                                                   | 123 |

| 9.3.1  | More on sweeps                                            | 124 |

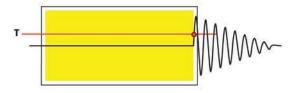

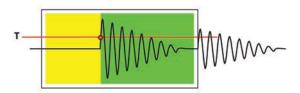

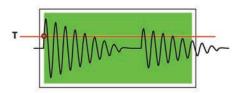

| 9.3.2  | Pre-trigger sweeps                                        | 125 |

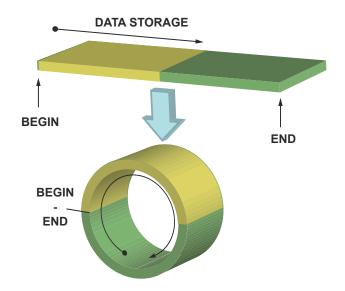

| 9.3.3  | More on continuous data storage                           | 128 |

| 9.4    | Time base                                                 | 129 |

| 10     | Digital Trigger Modes                                     | 130 |

| 10.1   | Introduction                                              | 130 |

| 10.2   | Understanding digital triggering                          | 131 |

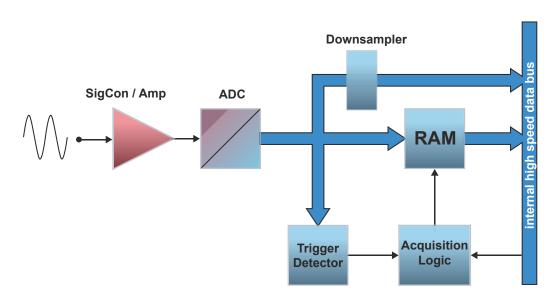

| 10.2.1 | Digital trigger detector                                  | 131 |

| 10.2.2 | Valid trigger conditions                                  | 133 |

| 10.3   | Trigger modes                                             | 135 |

| 10.3.1 | Basic trigger mode                                        | 135 |

| 10.3.2 | Dual trigger mode                                         | 136 |

| 10.3.3 | Trigger qualifier                                         | 137 |

| 10.4   | Recorder and system trigger                               | 138 |

| 10.5   | Channel alarm                                             | 140 |

| 11     | Interface/Controller                                      | 141 |

| 11.1   | Introduction                                              | 141 |

| 11.2   | Communication and control                                 | 142 |

| 11.2.1 | Network protocols and ports                               | 143 |

| 11.2.2 | Using the 1 Gbit option connections                       | 144 |

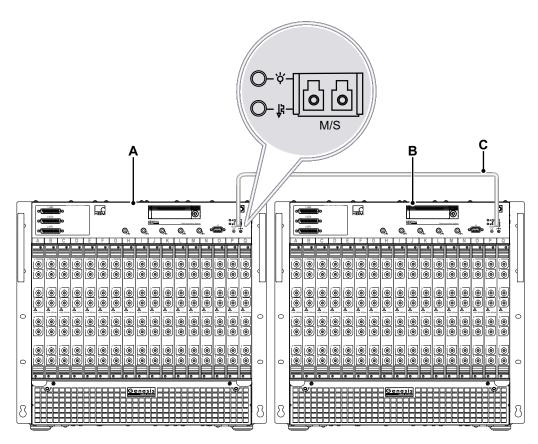

| 11.3   | Master/Sync connector                                     | 145 |

| 11.3.1 | Connecting the Master/Sync connector                      | 149 |

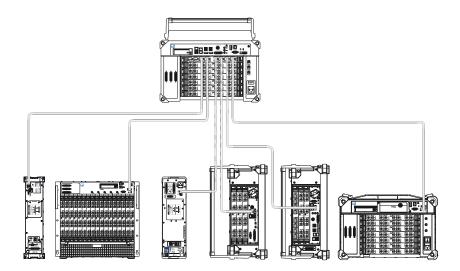

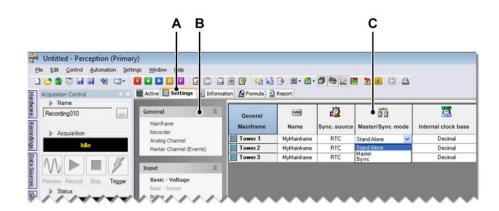

| 11.3.2 | Connecting multiple mainframes using the Master/Sync card | 149 |

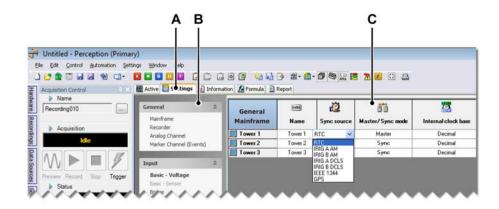

| 11.3.3 | Setting the Master/Sync operating modes                   | 151 |

| 11.3.4   | Synchronizing a Master/Sync setup to external time sources               | 153 |

|----------|--------------------------------------------------------------------------|-----|

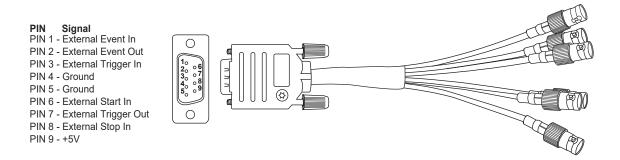

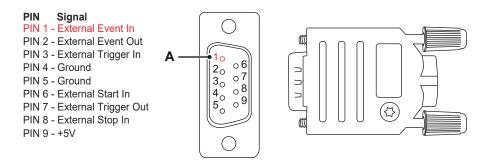

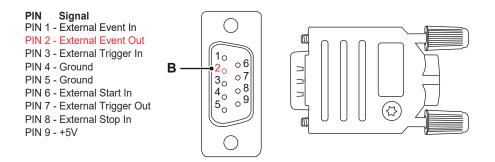

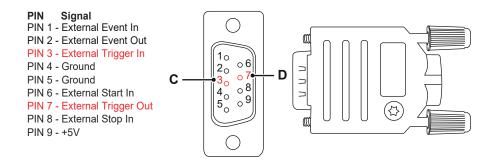

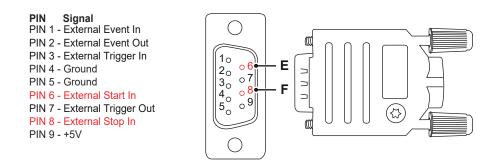

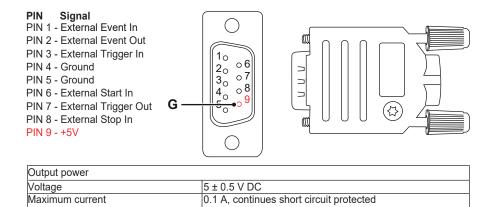

| 11.4     | I/O connector                                                            | 154 |

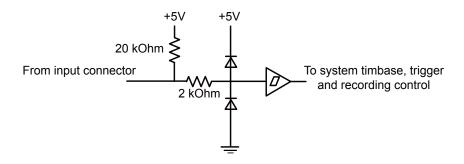

| 11.4.1   | I/O connector input overvoltage protection                               | 155 |

| 11.4.2   | I/O connector functions and connector pinning                            | 156 |

| 11.4.3   | External Start In/External Stop In                                       | 158 |

| 11.4.4   | External Event In use with RT-FDB                                        | 160 |

| 11.5     | Option - Removable Solid State Drive (SSD)                               | 161 |

| 11.6     | Option - Optical 1 Gbit Ethernet interface                               | 163 |

| 11.7     | Option - 10 Gbit Ethernet interface (SFP+ Module)                        | 165 |

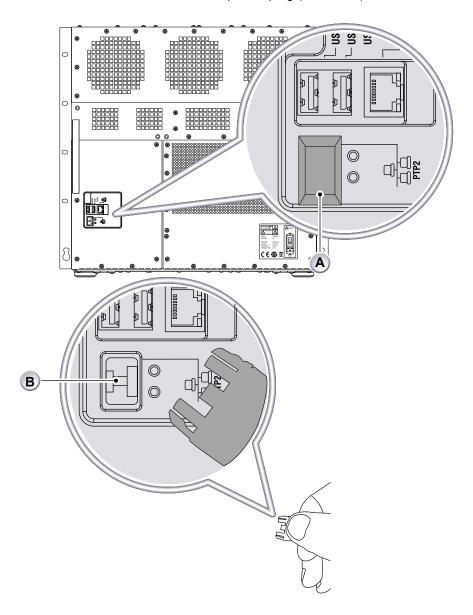

| 11.7.1   | Installing a 1 Gbit SFP/10 Gbit SFP+ Module                              | 172 |

| 11.7.1.1 | Introduction                                                             | 172 |

| 11.7.1.2 | Warnings                                                                 | 173 |

| 11.7.1.3 | Installation steps                                                       | 174 |

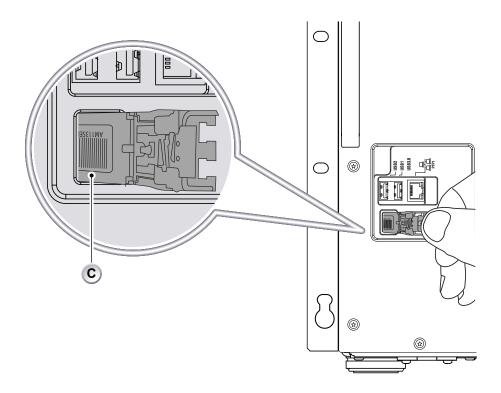

| 11.7.2   | Removing a 1 Gbit SFP/10 Gbit SFP+ Module                                | 177 |

| 11.8     | Option - EtherCAT®                                                       | 178 |

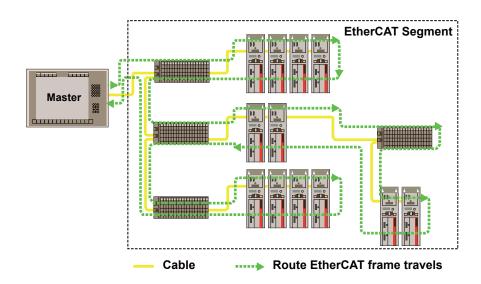

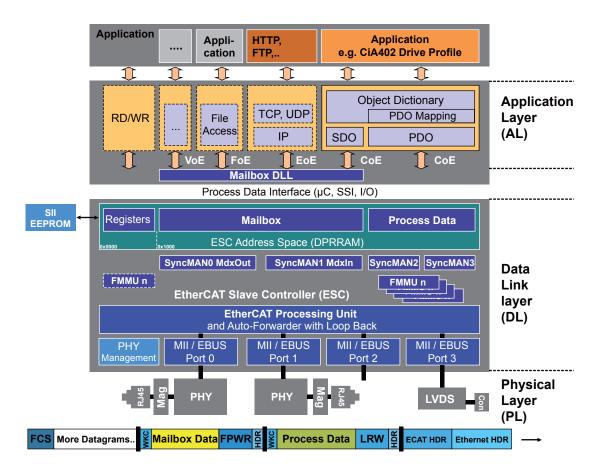

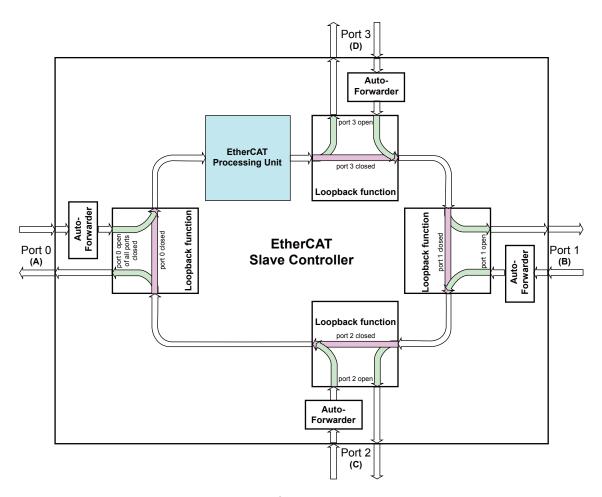

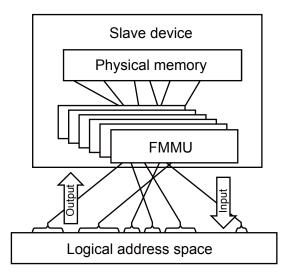

| 11.8.1   | EtherCAT® generic principles                                             | 179 |

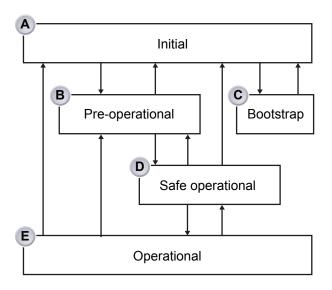

| 11.8.2   | EtherCAT® Slave Stack                                                    | 180 |

| 11.8.3   | Physical Layer                                                           | 181 |

| 11.8.4   | Data Link Layer                                                          | 181 |

| 11.8.5   | Application Layer                                                        | 183 |

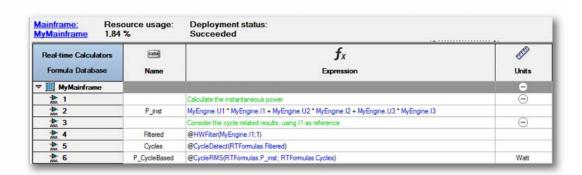

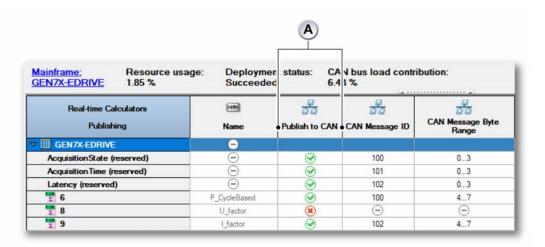

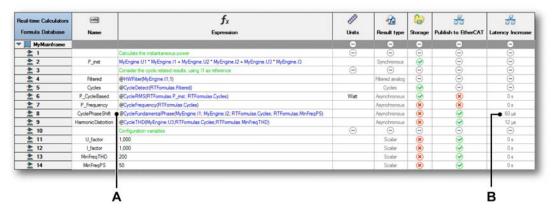

| 11.8.6   | Setting up fieldbus output channels in GEN series mainframes             | 185 |

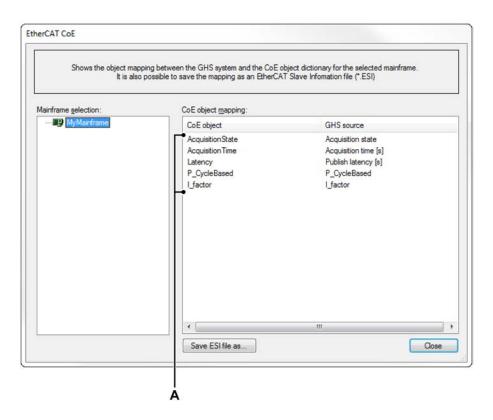

| 11.8.6.1 | Real-time formula database                                               | 185 |

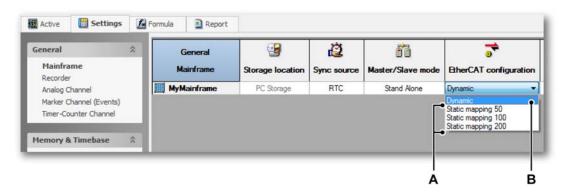

| 11.8.7   | Selecting the appropriate EtherCAT® configuration                        | 187 |

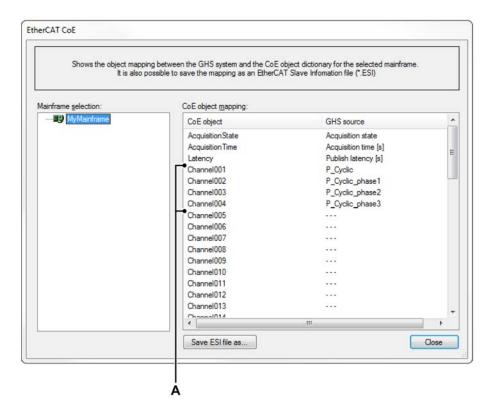

| 11.8.7.1 | Static mode                                                              | 187 |

| 11.8.7.2 | Dynamic mode                                                             | 189 |

| 11.8.8   | CoE Object layout                                                        | 190 |

| 11.8.9   | EtherCAT® timing aspects                                                 | 191 |

| 11.8.10  | Fieldbus timing aspects                                                  | 192 |

| 11.8.11  | Aligning fieldbus latencies over multiple mainframes                     | 193 |

| 11.8.12  | Supported EtherCAT® masters                                              | 194 |

| 11.8.13  | EtherCAT® interfacing                                                    | 194 |

| 11.8.14  | Troubleshooting                                                          | 197 |

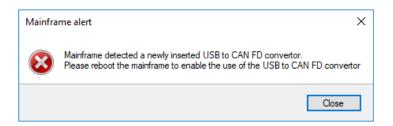

| 11.9     | Option - CAN FD out                                                      | 198 |

| 11.9.1   | Option - USB to CAN FD out                                               | 198 |

| 11.9.1.1 | Status LED of USB to CAN FD converter                                    | 199 |

| 11.9.2   | Option carrier card with integrated CAN FD controller (Customer special) | 200 |

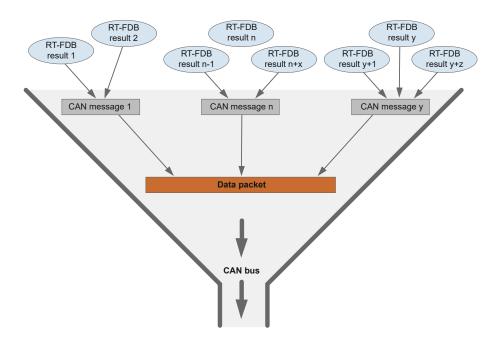

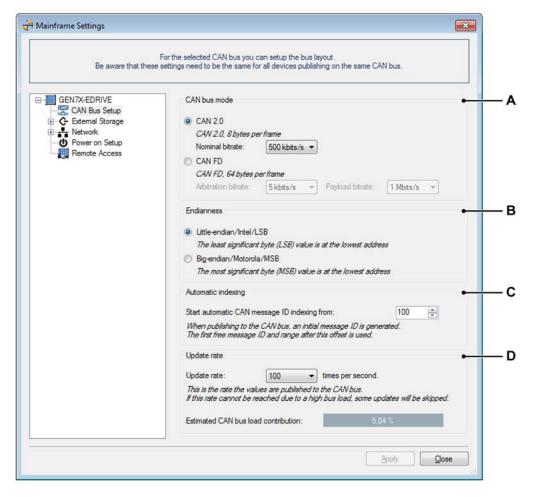

| 11.9.3   | CAN generic principles                                                   | 201 |

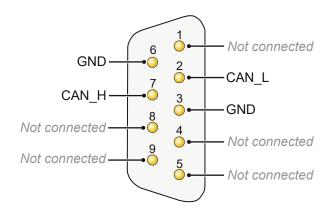

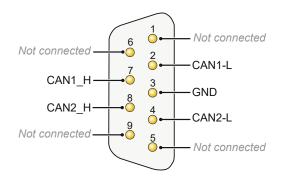

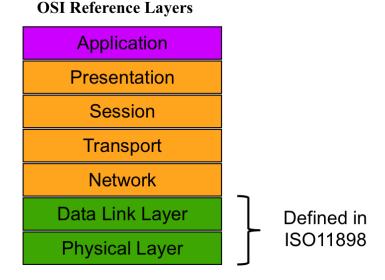

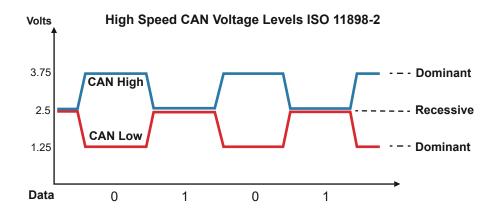

| 11.9.4    | Physical layer                                                          | 202 |

|-----------|-------------------------------------------------------------------------|-----|

| 11.9.5    | Data link layer                                                         | 203 |

| 11.9.6    | Application layer                                                       | 205 |

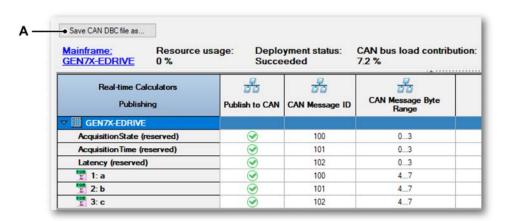

| 11.9.7    | Setting up CAN channels in Genesis                                      | 205 |

| 11.9.8    | Selecting the appropriate CAN configuration                             | 206 |

| 11.9.9    | CAN DBC file                                                            | 208 |

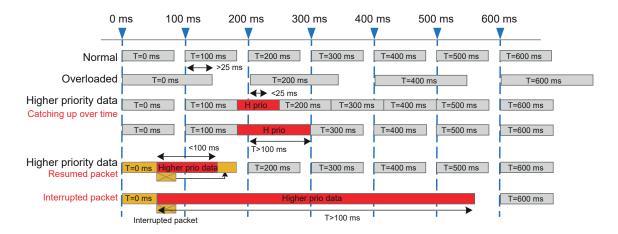

| 11.9.10   | CAN timing aspects                                                      | 210 |

| 11.9.11   | More CAN timing aspects                                                 | 210 |

| 11.9.12   | Working with CAN out                                                    | 211 |

| 11.9.13   | CAN Trouble-shooting                                                    | 212 |

| 12        | Input Cards                                                             | 213 |

| 12.1      | Available input cards                                                   | 213 |

| 12.2      | GN310B (2 MS/s), GN311B (200kS/s) Power Analyzer input cards            | 216 |

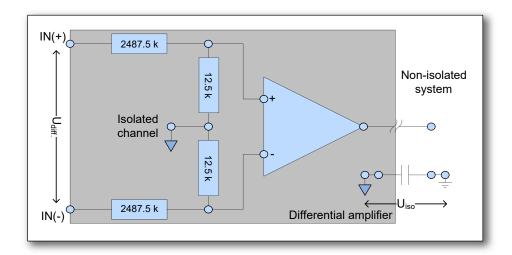

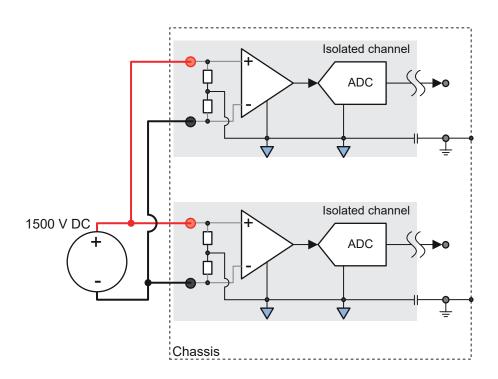

| 12.2.1    | Measuring voltages                                                      | 217 |

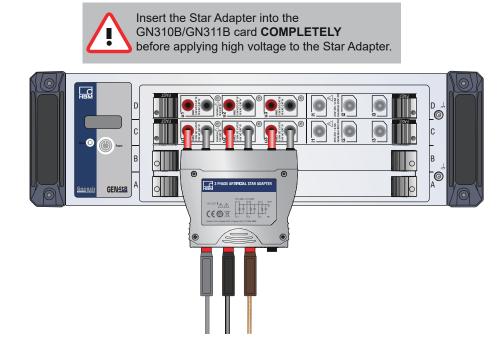

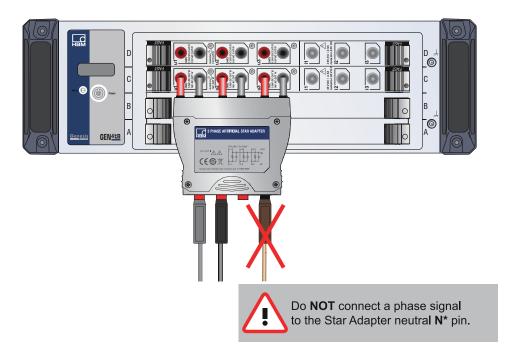

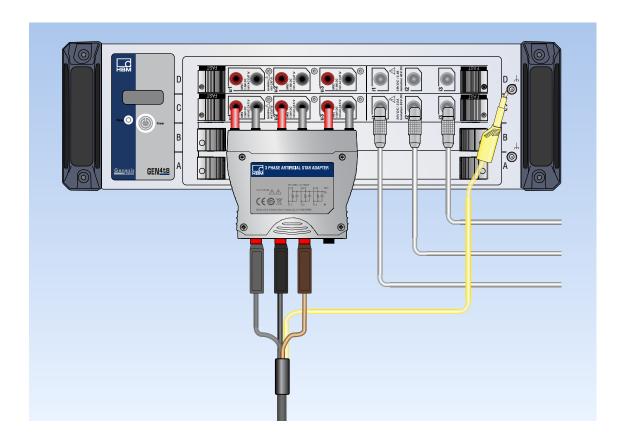

| 12.2.2    | Connecting 3 Phase Artificial Star Adapter                              | 221 |

| 12.2.3    | Measuring currents                                                      | 223 |

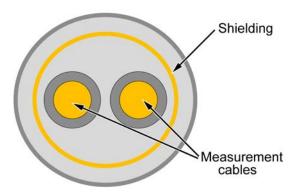

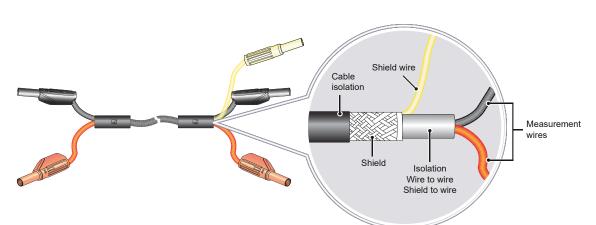

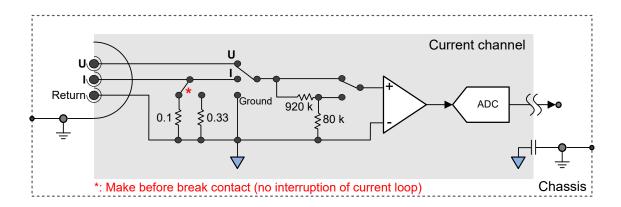

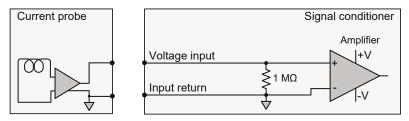

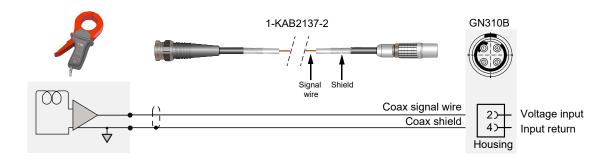

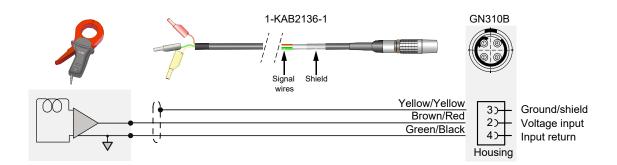

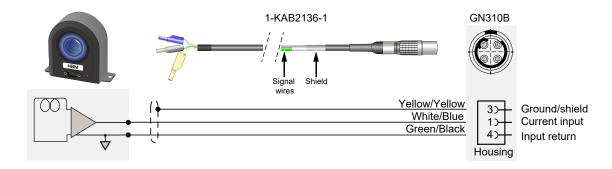

| 12.2.3.1  | GN310B/GN311B: Current Channel: Voltage mode and cabling                | 225 |

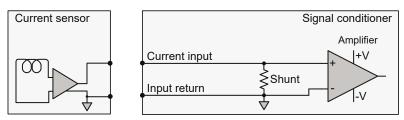

| 12.2.3.2  | GN310B/GN311B: Current Channel: Current mode and cabling                | 226 |

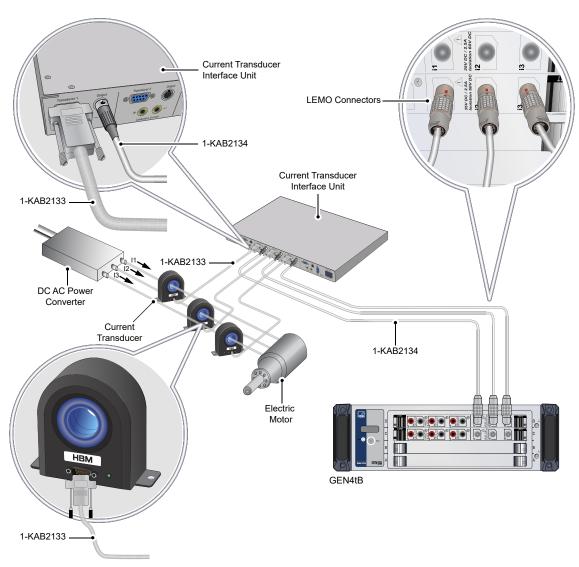

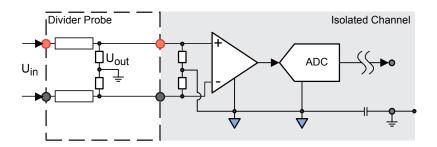

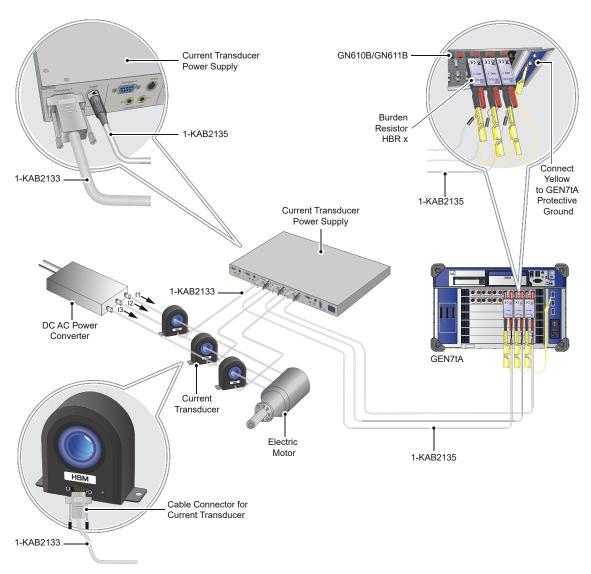

| 12.2.4    | Connecting HBM current transducers                                      | 227 |

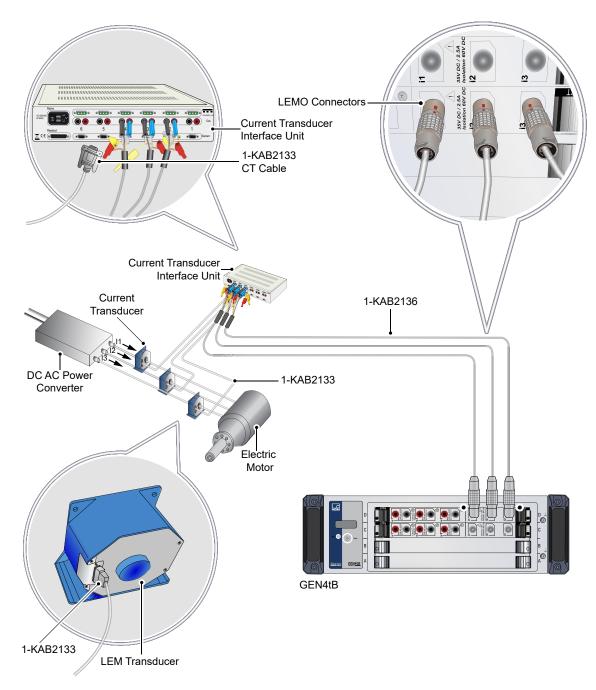

| 12.2.5    | Connecting LEM current transducers                                      | 228 |

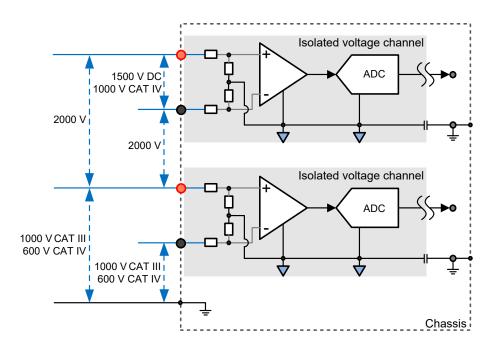

| 12.2.6    | Understanding the GN310B/GN311B category rating                         | 229 |

| 12.2.6.1  | Safety according to the harmonized standard                             | 229 |

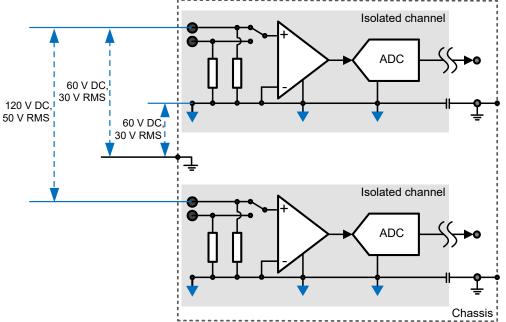

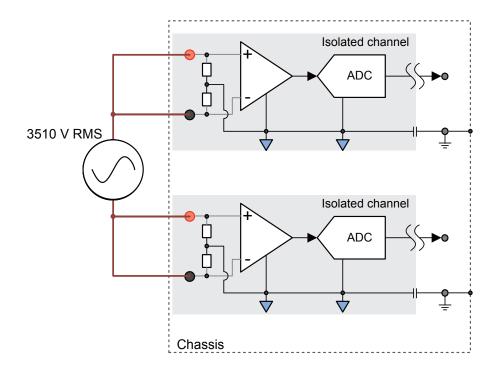

| 12.2.7    | Understanding the GN310B/GN311B high voltage input                      | 231 |

| 12.2.8    | GN310B/GN311B Isolation Voltage channel                                 | 232 |

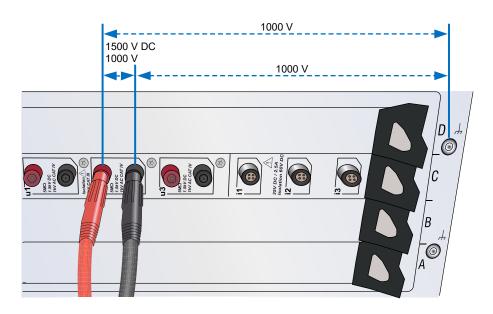

| 12.2.8.1  | Voltage Channel - Maximum voltage overview                              | 233 |

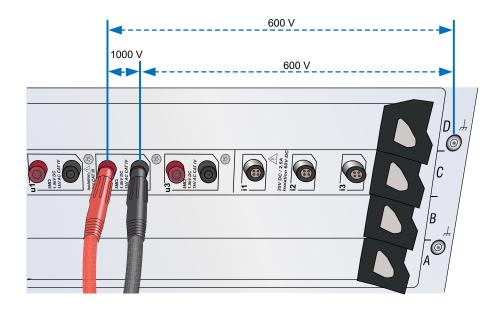

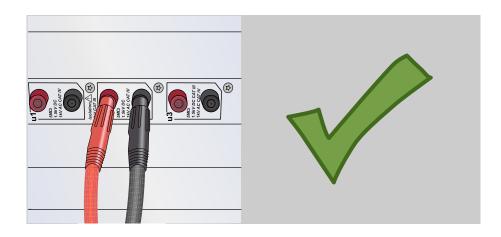

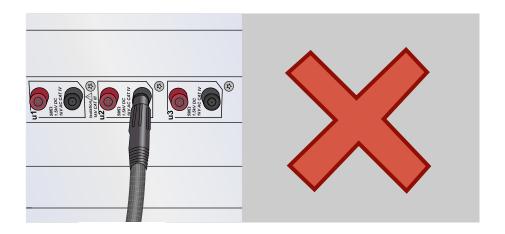

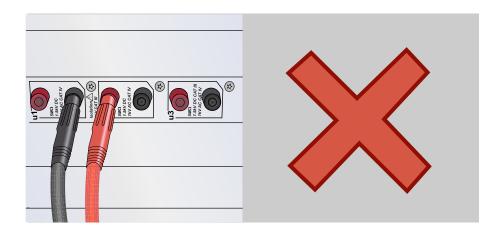

| 12.2.8.2  | Voltage Channel - Safe and unsafe connections                           | 235 |

| 12.2.9    | GN310B/GN311B Isolation Current channel                                 | 237 |

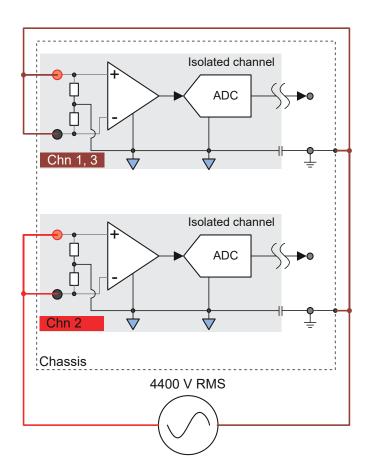

| 12.2.10   | GN310B/GN311B type testing of the HV channels                           | 238 |

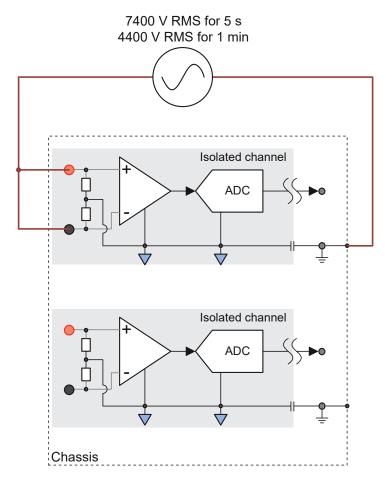

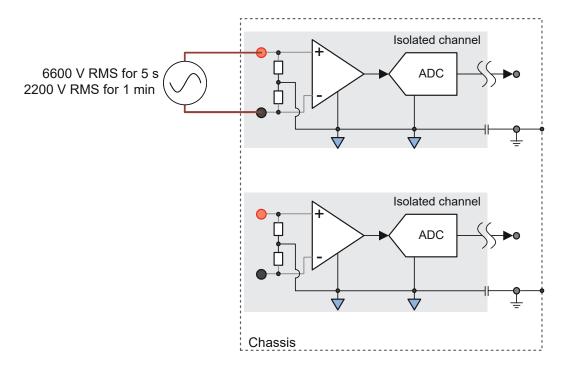

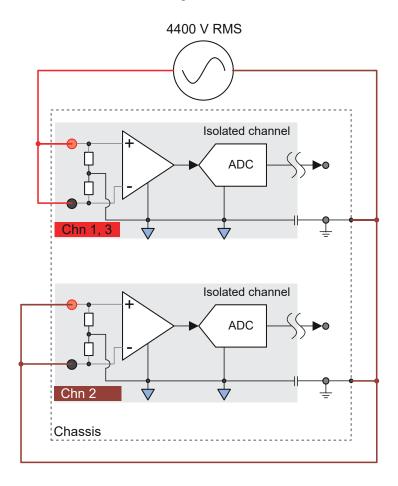

| 12.2.10.1 | Channel to chassis voltages (and test voltages)                         | 238 |

| 12.2.10.2 | Within high voltage channel isolation test (harmonized standard)        | 239 |

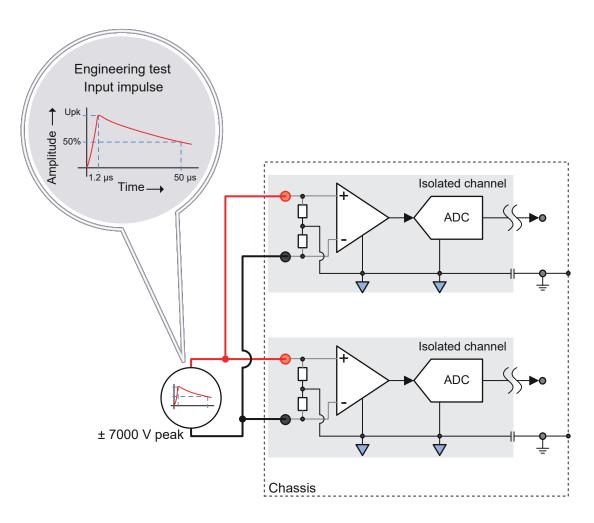

| 12.2.10.3 | High potential test                                                     | 240 |

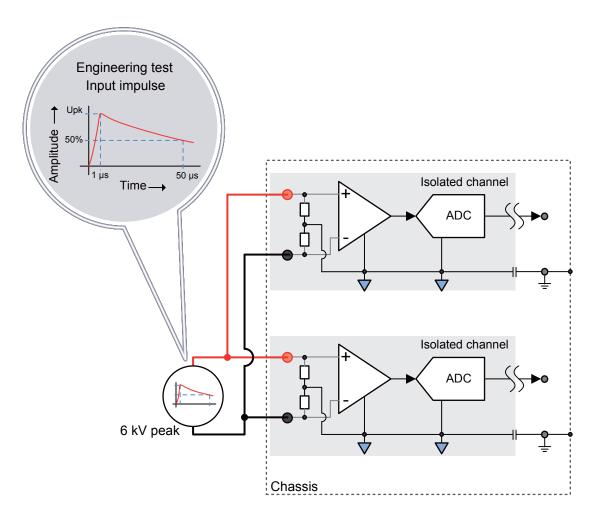

| 12.2.10.4 | Engineering tests                                                       | 242 |

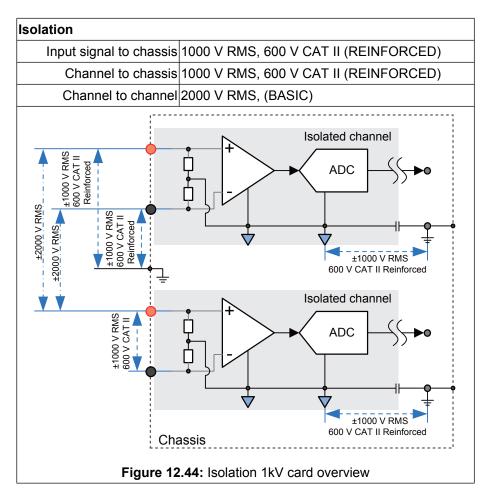

| 12.3      | Isolated 1kV input cards                                                | 243 |

| 12.3.1    | GN610B, Isolated 1kV 2MS/s input card with real-time formula database   | 243 |

| 12.3.2    | GN611B, Isolated 1kV 200kS/s input card with real-time formula database | 244 |

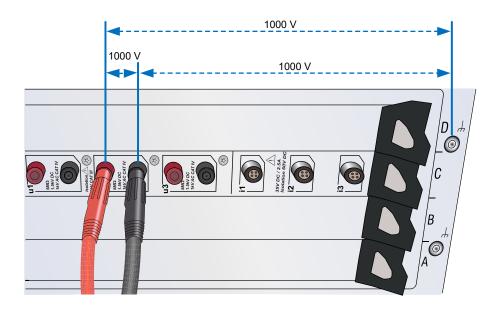

| 12.3.3    | Using the GN610B/GN611B                                                 | 245 |

| 12.3.4    | Understanding the GN610B/GN611B category rating                         | 249 |

| 12.3.5   | Understanding the GN610B/GN611B input                       | 249 |

|----------|-------------------------------------------------------------|-----|

| 12.3.6   | Using the High Precision Differential Probe                 | 252 |

| 12.3.7   | Measuring currents                                          | 255 |

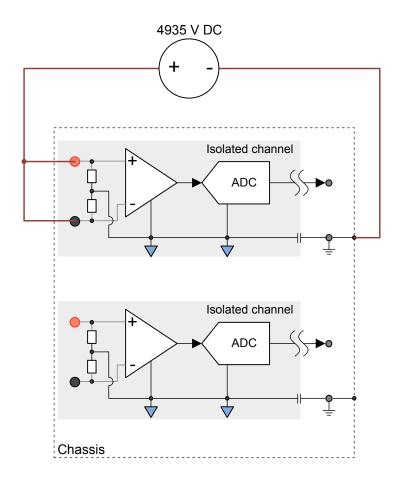

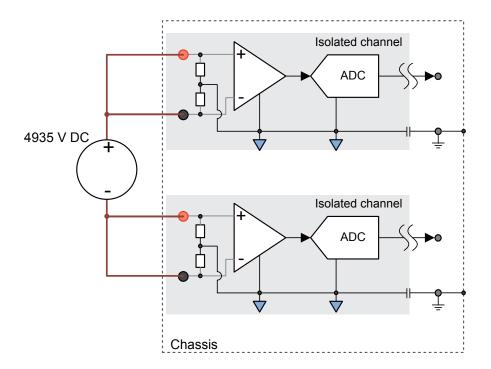

| 12.3.8   | GN610B/GN611B Isolation and type testing                    | 256 |

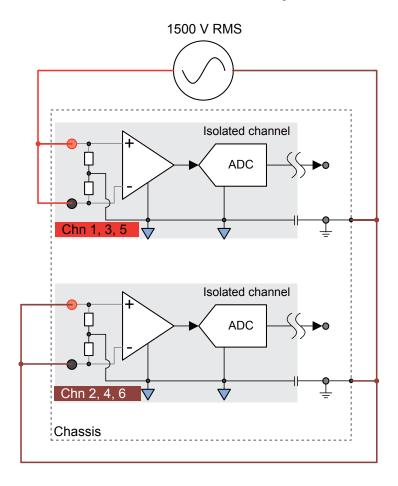

| 12.3.8.1 | Channel to chassis isolation test                           | 258 |

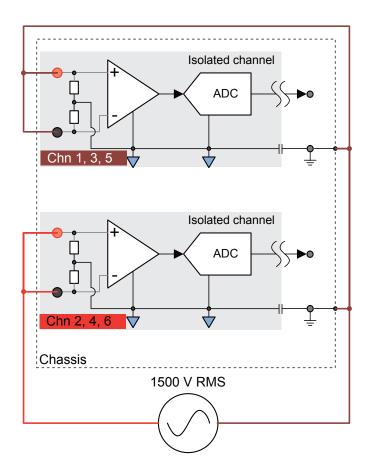

| 12.3.8.2 | Channel to channel isolation test                           | 260 |

| 12.3.8.3 | High potential test                                         | 262 |

| 12.3.8.4 | Engineering tests                                           | 264 |

| 12.3.9   | GN610B/GN611B protection mechanisms                         | 265 |

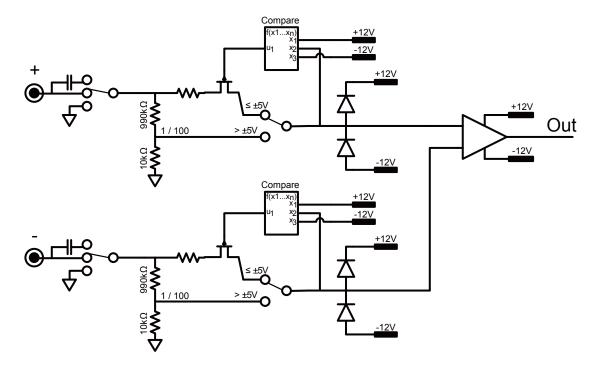

| 12.3.9.1 | Overvoltage and current protection                          | 265 |

| 12.3.9.2 | GN610B/GN611B input overload protection                     | 265 |

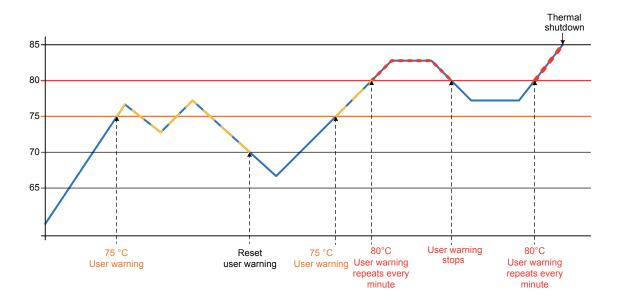

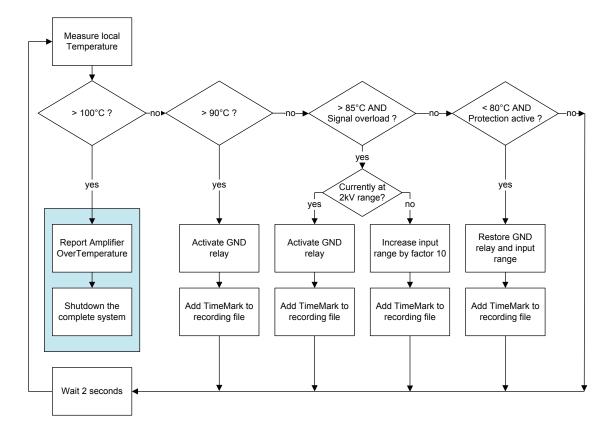

| 12.3.9.3 | Thermal monitor of the input channels                       | 267 |

| 12.3.9.4 | Thermal shutdown in critical conditions                     | 268 |

| 12.3.9.5 | Restore range selected by user automatically                | 269 |

| 12.4     | Isolated Basic/IEPE cards                                   | 270 |

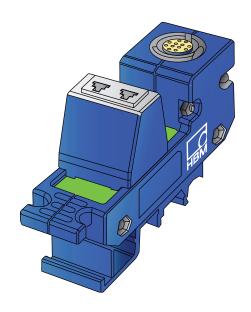

| 12.4.1   | GN815, Isolated Basic/IEPE 2MS/s input card                 | 270 |

| 12.4.2   | GN816, Isolated Basic/IEPE 200kS/s input card               | 271 |

| 12.4.3   | Using the GN815 and GN816                                   | 272 |

| 12.4.4   | Understanding the GN815 and GN816 isolation                 | 274 |

| 12.4.5   | Understanding the GN815 and GN816 input                     | 275 |

| 12.4.5.1 | Characteristics per channel:                                | 276 |

| 12.4.5.2 | Using probes:                                               | 276 |

| 12.4.6   | GN815 and GN816 Input overload protection                   | 277 |

| 12.4.6.1 | Thermal monitor of the input channels                       | 278 |

| 12.4.6.2 | Restore range selected by user automatically                | 278 |

| 12.4.6.3 | Thermal shutdown in critical conditions                     | 279 |

| 12.5     | Basic high speed input card                                 | 280 |

| 12.5.1   | GN8101B/GN8102B/GN8103B, Basic 250, 100, 25 M/s input cards | 280 |

| 12.6     | High resolution universal input card                        | 281 |

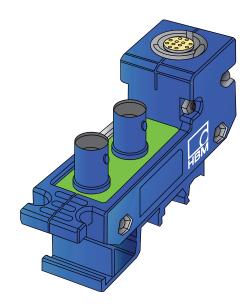

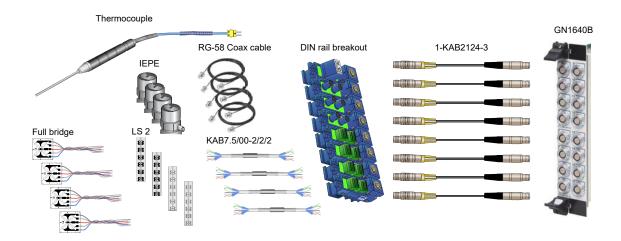

| 12.6.1   | GN840/GN1640 Universal 500 kS/s 8/16 channel input cards    | 281 |

| 12.6.1.1 | Supported sensor modes                                      | 282 |

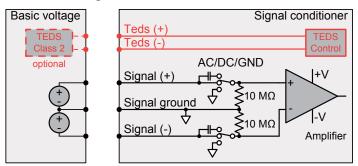

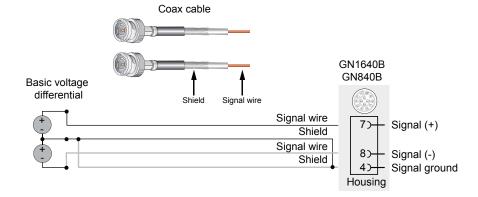

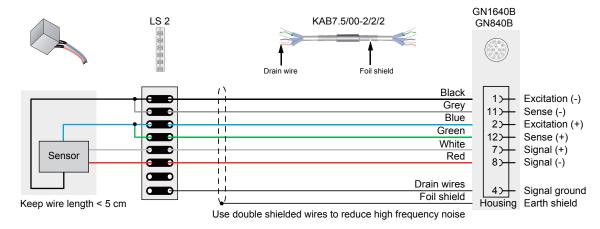

| 12.6.2   | Basic mode and cabling                                      | 283 |

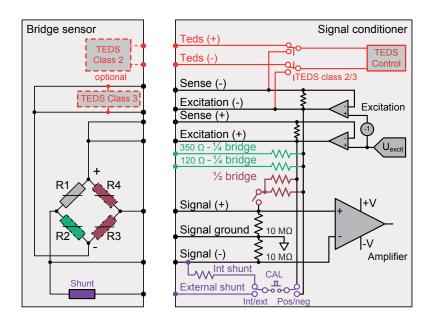

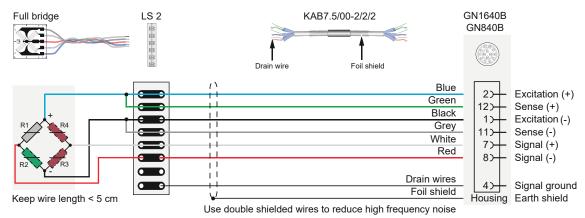

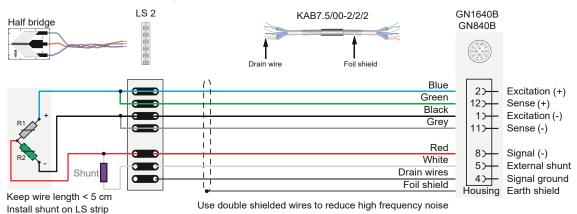

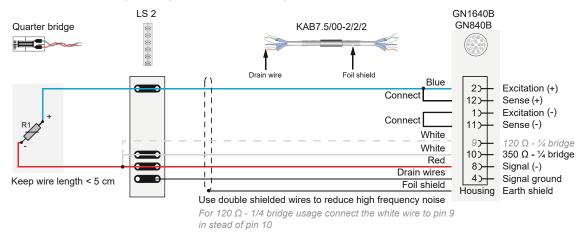

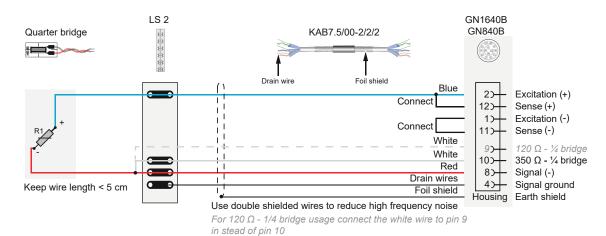

| 12.6.3   | Bridge mode and cabling                                     | 284 |

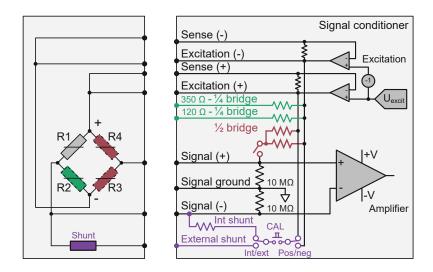

| 12.6.3.1 | Bridge amplifier configuration                              | 284 |

| 12.6.3.2 | Bridge completion                                           | 284 |

| 12.6.3.3 | Sense lines                                                 | 285 |

| 12.6.3.4 | Bridge balance                                              | 285 |

| 12.6.3.5 | Shunt calibration                                           | 285 |

|----------|-------------------------------------------------------------|-----|

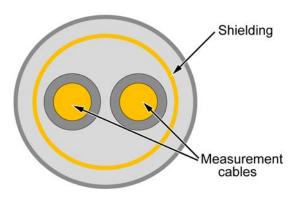

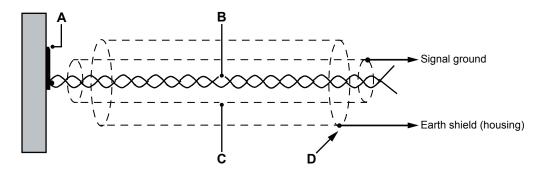

| 12.6.3.6 | Shielding and immunity increase                             | 285 |

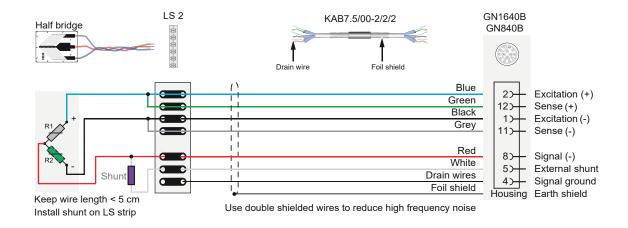

| 12.6.3.7 | Various bridge configurations                               | 287 |

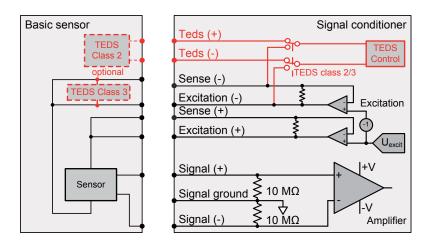

| 12.6.4   | Basic sensor and cabling                                    | 288 |

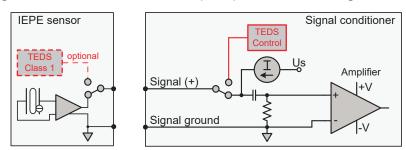

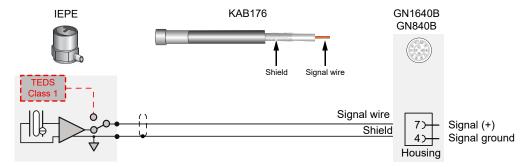

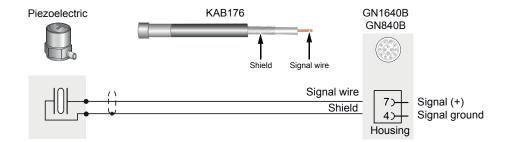

| 12.6.5   | Integrated Electronic Piezoelectric (IEPE) mode and cabling | 289 |

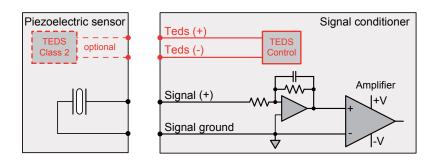

| 12.6.6   | Piezoelectric (Charge) mode and cabling                     | 290 |

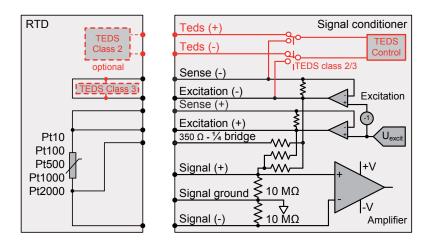

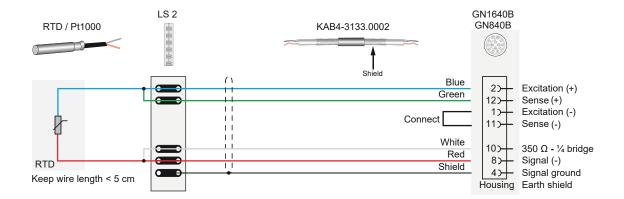

| 12.6.7   | Resistive Temperature Detectors (RTD) mode and cabling      | 291 |

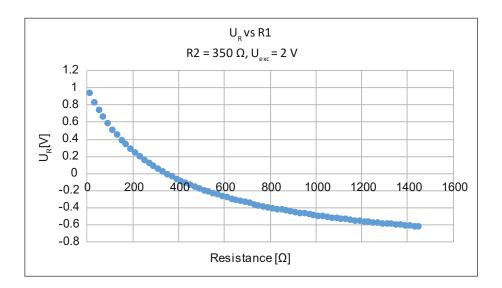

| 12.6.8   | Resistance mode                                             | 292 |

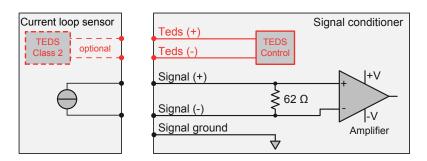

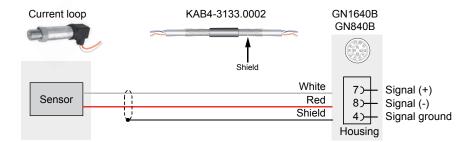

| 12.6.9   | Current loop mode and cabling                               | 295 |

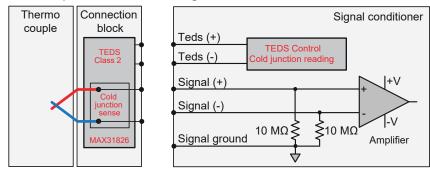

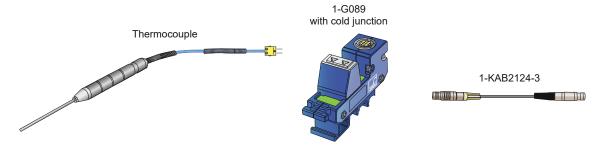

| 12.6.10  | Thermocouple mode and cabling                               | 296 |

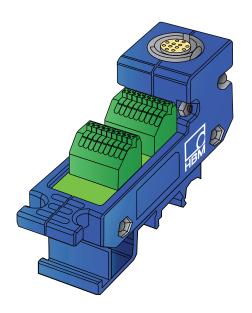

| 12.6.11  | DIN rail breakout                                           | 297 |

| 12.6.12  | Flexible wiring                                             | 300 |

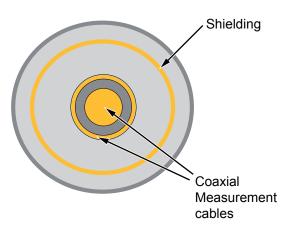

| 12.7     | Optical fiber isolated input card                           | 301 |

| 12.7.1   | GN1202B, Optical fiber isolated 100 MS/s input card         | 301 |

| 12.8     | High resolution IEPE and Charge input cards                 | 303 |

| 12.8.1   | GN3210 IEPE and charge 250 kS/s input card                  | 303 |

| 12.8.2   | GN3211 basic 20 kS/s input card                             | 305 |

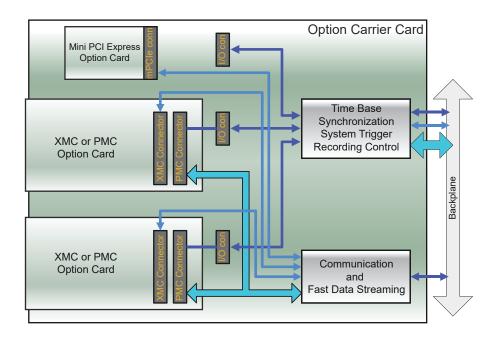

| 13       | Option Cards                                                | 307 |

| 13.1     | Option Carrier Card (OCC)                                   | 307 |

| 13.1.1   | Option cards supported                                      | 308 |

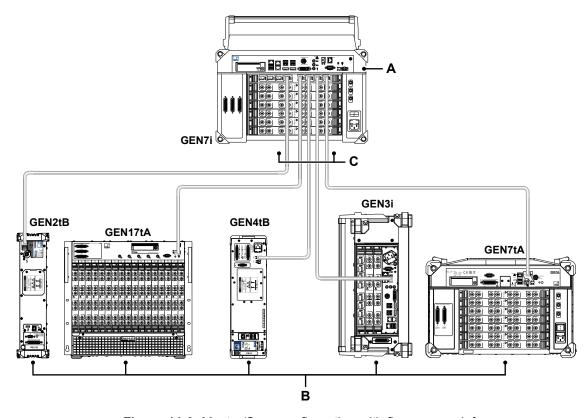

| 14       | GEN series Synchronization Methods                          | 309 |

| 14.1     | GEN series synchronization methods compared                 | 309 |

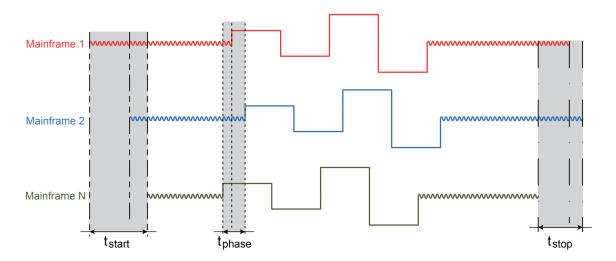

| 14.1.1   | Signal phase shift synchronization                          | 309 |

| 14.1.2   | Trigger synchronization                                     | 311 |

| 14.1.3   | Absolute time of day synchronization                        | 312 |

| 14.1.4   | Start/Stop synchronization                                  | 314 |

| 14.1.5   | Synchronization specification overview                      | 315 |

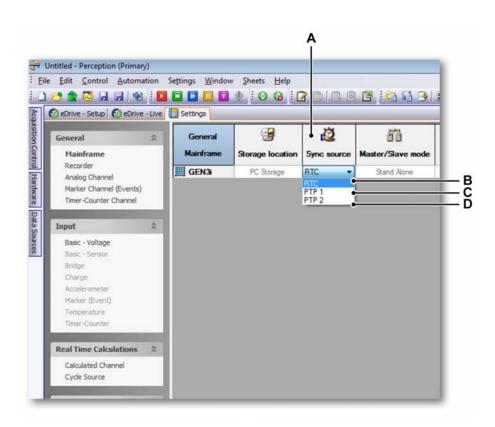

| 14.2     | PTP                                                         | 317 |

| 14.2.1   | PTP technology background(1)                                | 317 |

| 14.2.1.1 | Architecture                                                | 317 |

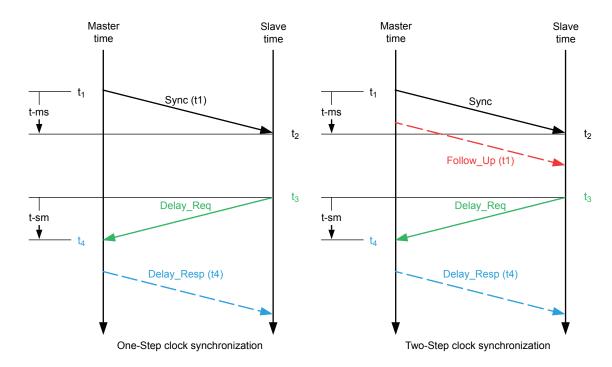

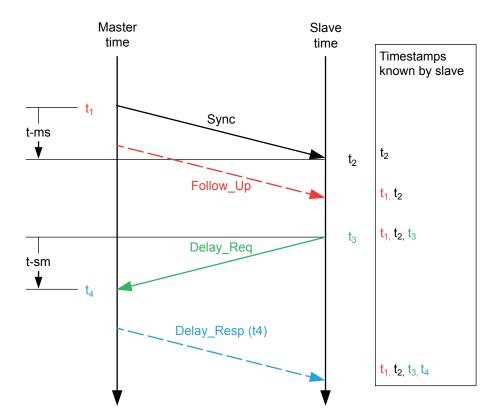

| 14.2.2   | PTP Protocol details                                        | 318 |

| 14.2.3   | Best master clock algorithm (BMC)                           | 319 |

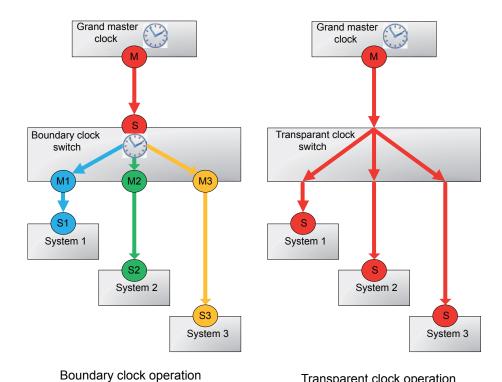

| 14.2.4   | PTP switch types                                            | 321 |

| 14.2.4.1 | Switches using boundary clocks                              | 322 |

| 14.2.4.2 | Switches using transparent clocks                           | 323 |

| 14.2.4.3 | End-to-End transparent clocks                               | 323 |

| 14.2.4.4 | Peer-to-Peer transparent clocks                             | 323 |

| 14.2.4.5 | One-Step and Two-Step clock synchronization                                   | 323 |

|----------|-------------------------------------------------------------------------------|-----|

| 14.2.5   | Transparent clock switch synchronization                                      | 325 |

| 14.2.5.1 | Message-based synchronization                                                 | 325 |

| 14.2.5.2 | Switch delays                                                                 | 328 |

| 14.2.6   | Common terms used in IEEE 1588                                                | 329 |

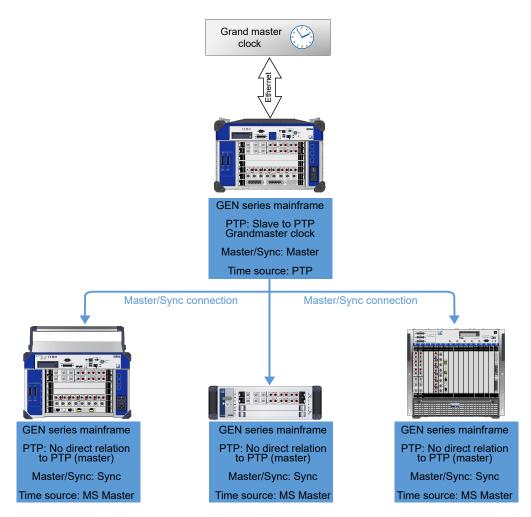

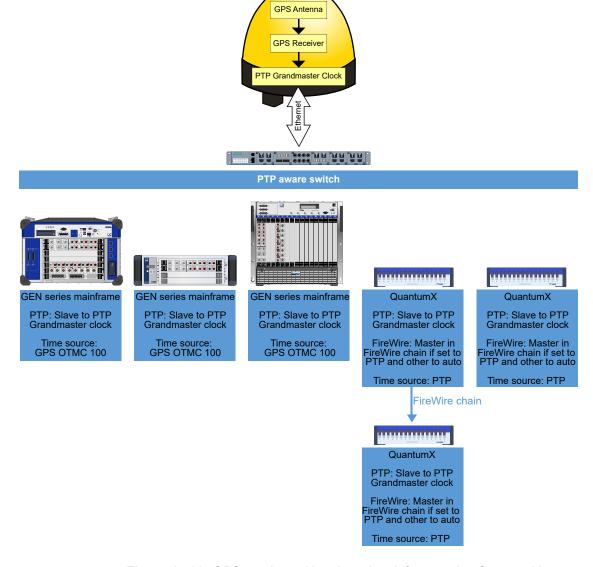

| 14.2.7   | PTP and Master/Sync                                                           | 330 |

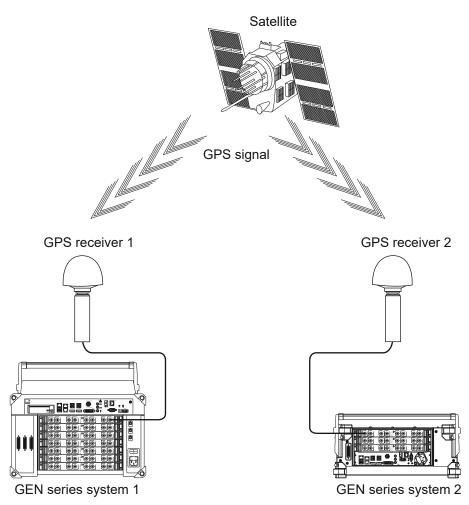

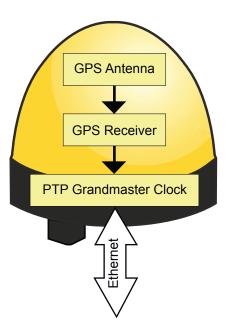

| 14.3     | GPS                                                                           | 332 |

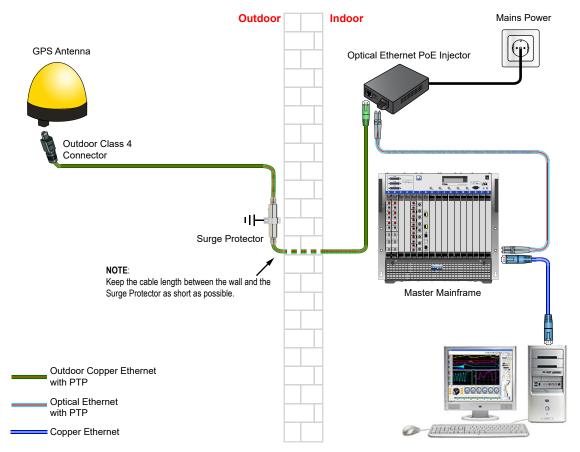

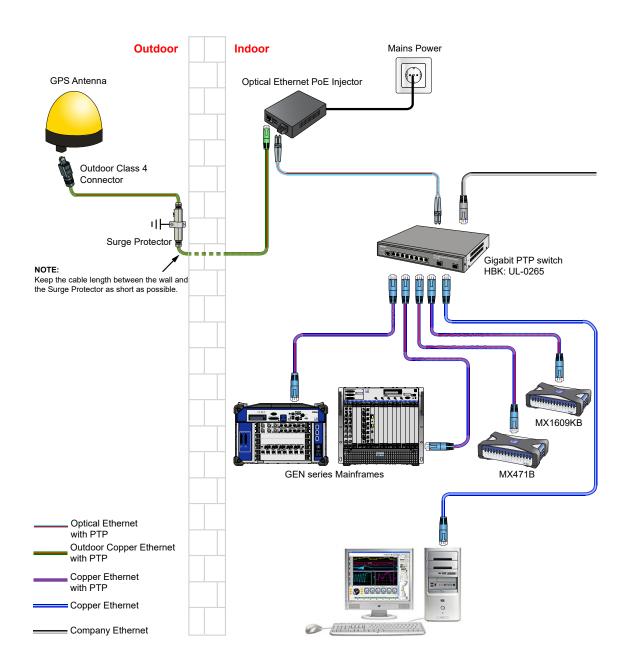

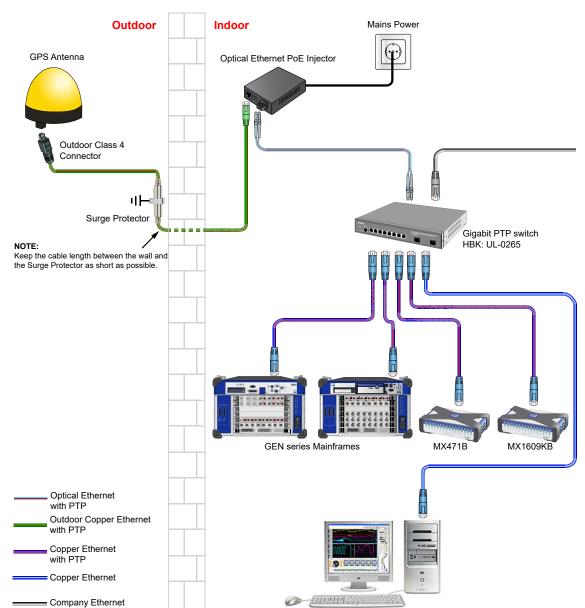

| 14.3.1   | Installation                                                                  | 332 |

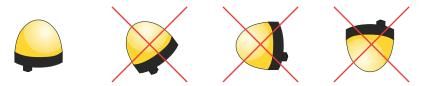

| 14.3.2   | Using the GPS antenna                                                         | 334 |

| 14.3.2.1 | Perception setup                                                              | 335 |

| 14.3.2.2 | Verify setup and installation                                                 | 338 |

| 14.3.2.3 | Status information                                                            | 338 |

| 14.3.2.4 | System topology                                                               | 338 |

| 14.3.2.5 | Recording information                                                         | 339 |

| 14.3.2.6 | Complex setups                                                                | 341 |

| 14.3.2.7 | Complex setup: G002B: GPS Receiver with Master/Sync connected Sync mainframes | 341 |

| 14.3.2.8 | Complex setup: G002B: GPS receiver with tethered mainframes plus QuantumX     | 346 |

| 14.3.3   | Setup comparison                                                              | 350 |

| 14.3.4   | GPS antenna placement                                                         | 351 |

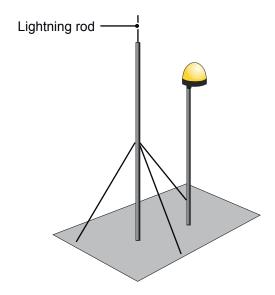

| 14.3.5   | GPS antenna lightning protection                                              | 353 |

| 14.3.6   | Trouble-shooting guide for G002B                                              | 354 |

| 14.4     | IRIG                                                                          | 355 |

| 14.4.1   | System overview                                                               | 355 |

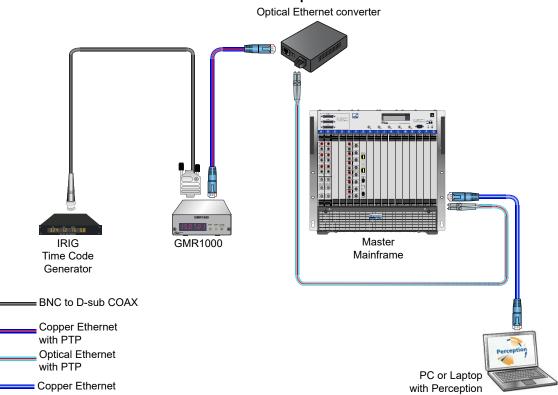

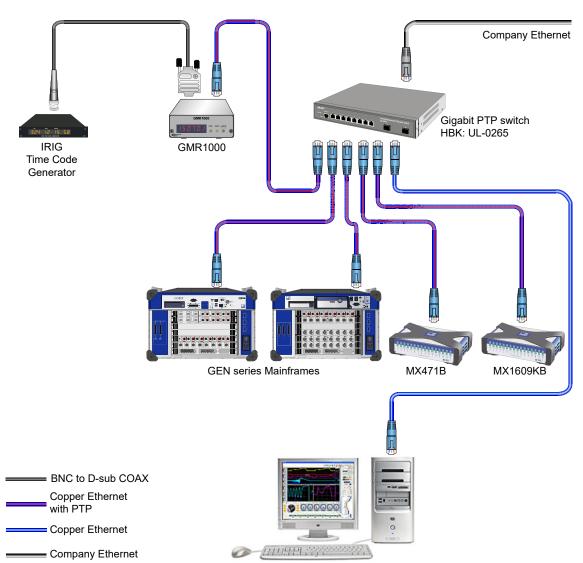

| 14.4.1.1 | G001B: Direct connection setup                                                | 355 |

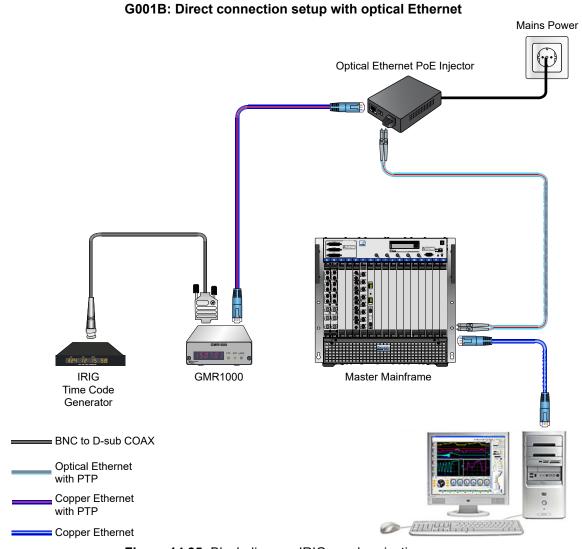

| 14.4.1.2 | G001B: Direct connection setup with optical Ethernet                          | 356 |

| 14.4.1.3 | G001B: IRIG to PTP with tethered mainframes plus QuantumX                     | 357 |

| 14.4.2   | Installation                                                                  | 358 |

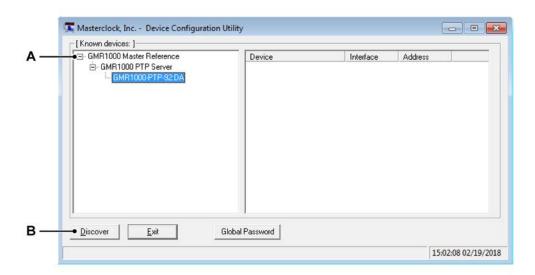

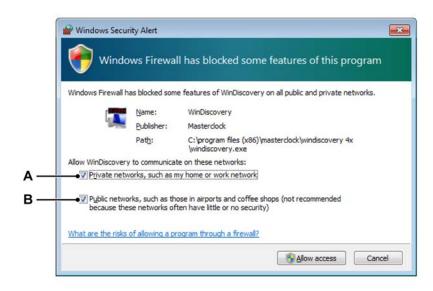

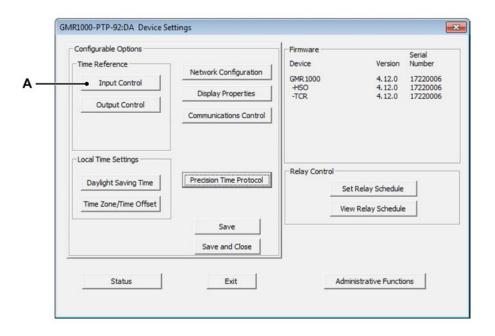

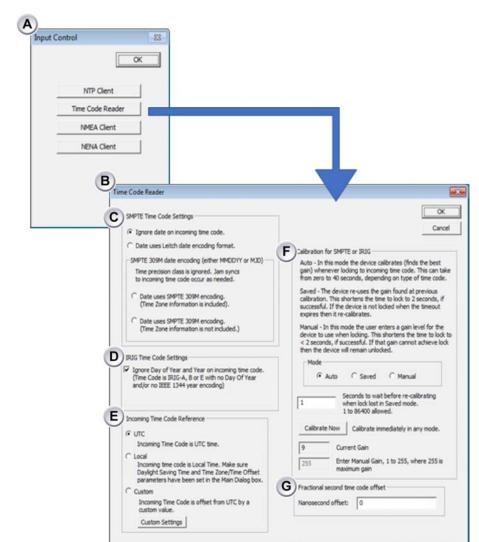

| 14.4.3   | Using the GMR1000 module                                                      | 359 |

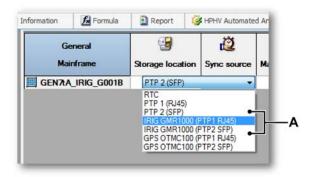

| 14.4.3.1 | Perception setup                                                              | 360 |

| 14.4.3.2 | Verify setup and installation                                                 | 363 |

| 14.4.3.3 | Status information                                                            | 363 |

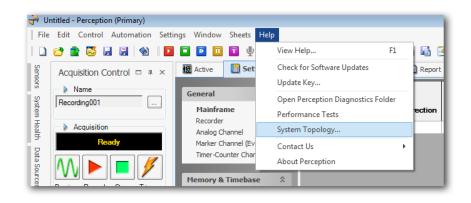

| 14.4.3.4 | System topology                                                               | 363 |

| 14.4.3.5 | Recording information                                                         | 364 |

| 14.4.4   | Trouble-shooting guide for G001B                                              | 366 |

| 15       | Understanding Inputs and Usage of Probes                                      | 367 |

| 15.1     | GEN series inputs                                                             | 367 |

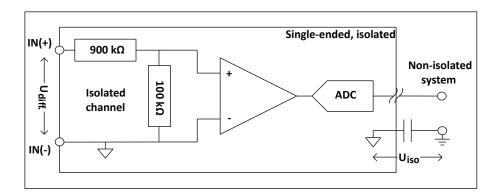

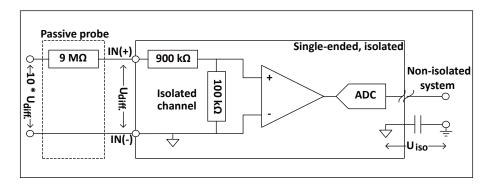

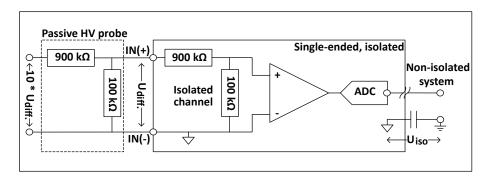

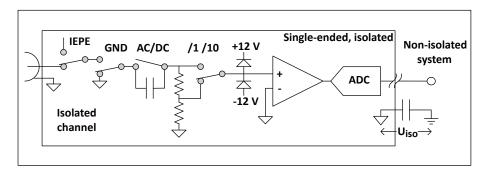

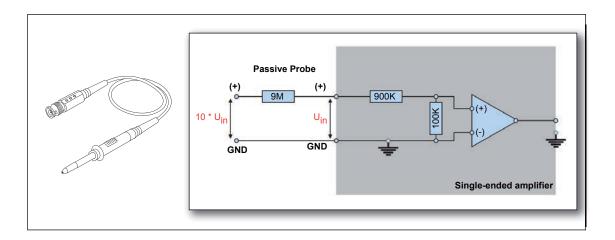

| 15.1.1   | Single-ended input                                                            | 368 |

| D.1    | Overview                                                        | 453        |  |

|--------|-----------------------------------------------------------------|------------|--|

| D      | Frequently Asked Questions                                      | 453        |  |

| C.9    | GPS OTMC 100 Trouble-shooting                                   | 432        |  |

| C.8    | IRIG GMR1000 Trouble-shooting                                   | 407        |  |

| C.7    | CAN Trouble-shooting                                            | 405        |  |

| C.6    | Master/Sync connection verification procedure                   | 403        |  |

| C.5    | Optical Network (SFP)                                           | 402        |  |

| C.4    | The Master/Sync connection does not synchronize                 | 401        |  |

| C.3    | Unexpected mainframe shutdown                                   | 400        |  |

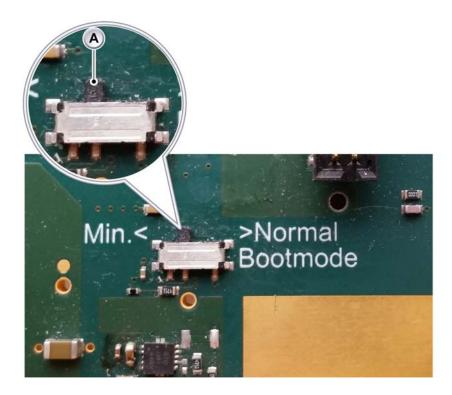

| C.2.1  | Boot recovery switch                                            | 397        |  |

| C.2    | Embedded Software upgrades                                      | 397        |  |

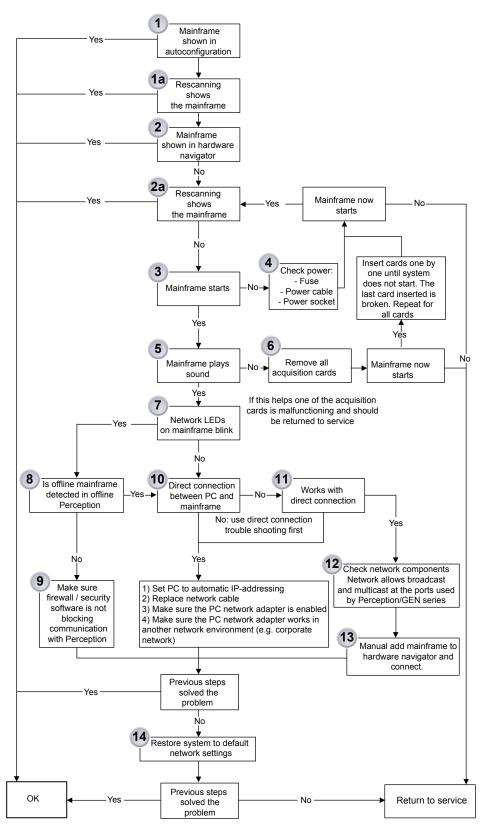

| C.1    | GEN17tA is not detected                                         | 392        |  |

| С      | Trouble-shooting                                                | 392        |  |

| B.2    | Calibration/verification                                        | 391        |  |

| B.1    | General - Service Information                                   | 390        |  |

| В      | Service Information                                             | 390        |  |

| A.4    | Cleaning                                                        | 389        |  |

| A.3    | Preventive air filter replacement                               | 388        |  |

| A.2.2  | Solid State Drive (SSD)                                         | 387        |  |

| A.2.1  | Hard disk drive                                                 | 387        |  |

| A.2    | Preventive drive replacement                                    | 387        |  |

| A.1    | Preventive maintenance                                          | 386        |  |

| A      | Maintenance                                                     | 386        |  |

| 15.4   | Current shunt measurements                                      | 385        |  |

| 15.3.3 | Probes and differential measurements                            | 384        |  |

| 15.3.2 | 10X Probes                                                      | 383        |  |

| 15.3.1 | 1X Probes                                                       | 381        |  |

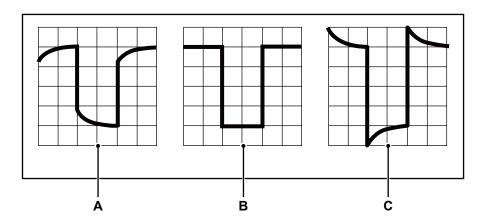

| 15.3   | Probe bandwidth calibration                                     | 381        |  |

| 15.2.4 | Active differential voltage probes                              | 380        |  |

| 15.2.3 | Passive, differential matched isolated voltage probes           | 379        |  |

| 15.2.2 | Passive, single-ended isolated voltage probes                   | 378        |  |

| 15.2.1 | Passive, single-ended voltage probes                            | 376        |  |

| 15.1.4 | GEN series voltage probe types                                  | 373<br>375 |  |

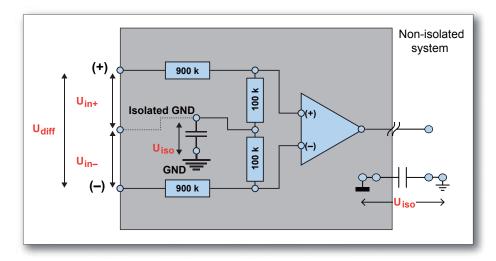

| 15.1.4 | Isolated balanced differential input                            |            |  |

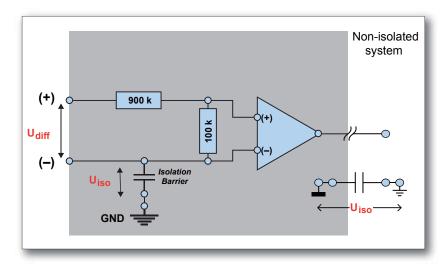

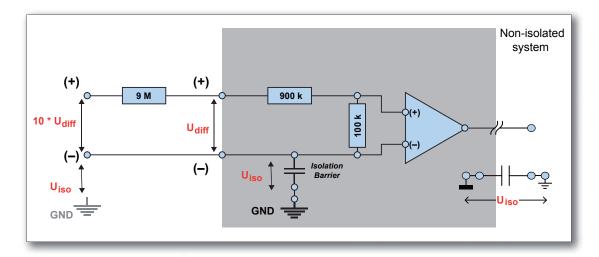

| 15.1.2 | Isolated single-ended or Isolated unbalanced differential input |            |  |

| 15.1.2 | Balanced differential input                                     | 370        |  |

| E        | Rack Mount Instructions                                                          | 454           |

|----------|----------------------------------------------------------------------------------|---------------|

| E.1      | Mount GEN17tA in a 19-inch rack                                                  | 454           |

| F        | PTP synchronization                                                              | 455           |

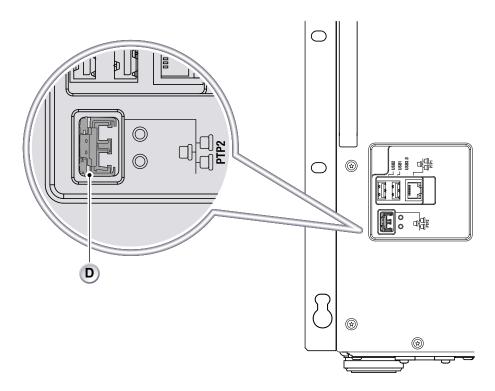

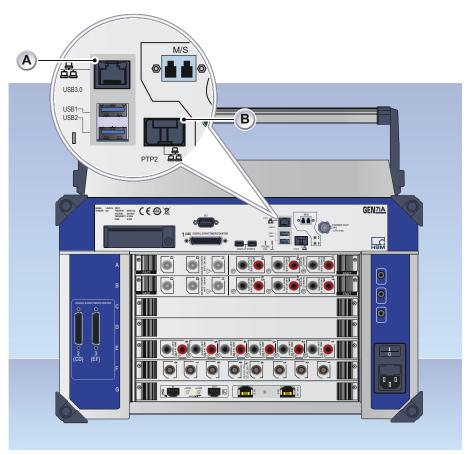

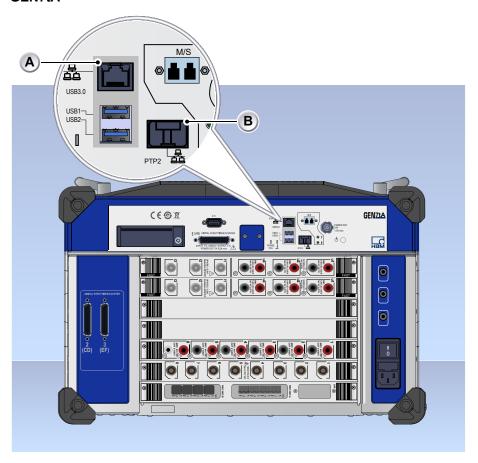

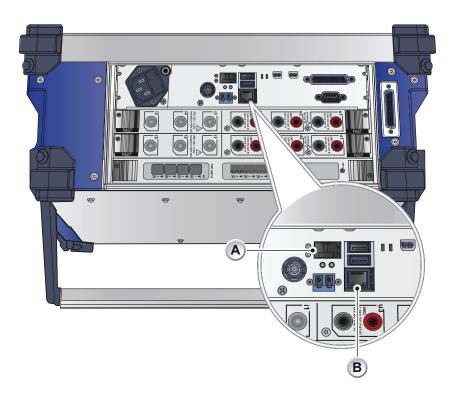

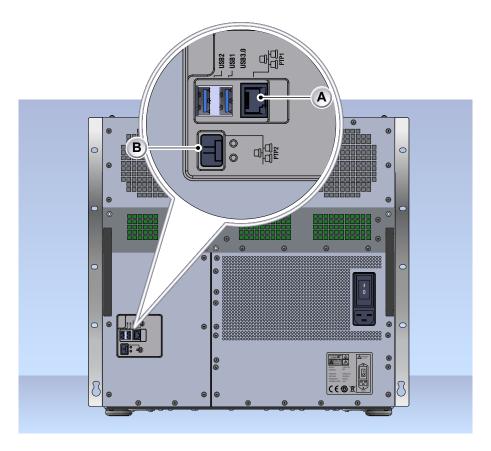

| F.1      | Mainframe PTP connections                                                        | 455           |

| F.1.1    | GEN7i                                                                            | 455           |

| F.1.2    | GEN7iA                                                                           | 456           |

| F.1.3    | GEN7tA                                                                           | 457           |

| F.1.4    | GEN2tB                                                                           | 458           |

| F.1.5    | GEN4tB                                                                           | 459           |

| F.1.6    | GEN3i                                                                            | 460           |

| F.1.7    | GEN3iA                                                                           | 461           |

| F.1.8    | GEN17tA                                                                          | 462           |

| F.2      | Perception settings                                                              | 463           |

| F.3      | Synchronizing GEN series and QuantumX using PTP                                  | 464           |

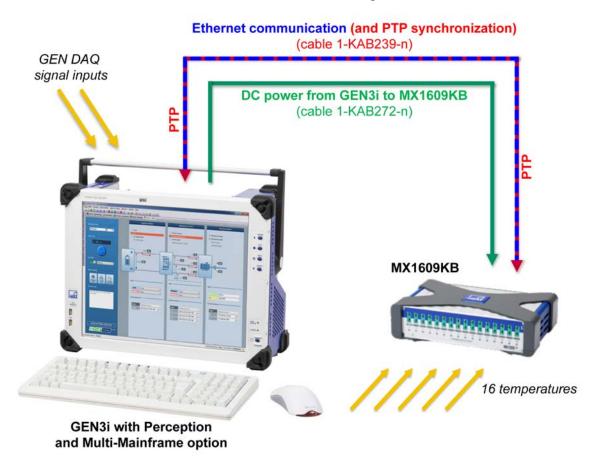

| F.3.1    | GEN3i/GEN3iA/GEN7i/GEN7iA with single QuantumX "B" version module                | 464           |

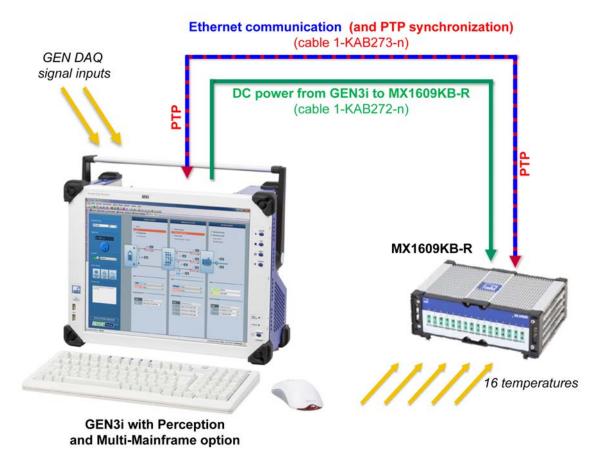

| F.3.2    | GEN3i/GEN3iA/GEN7i/GEN7iA with single SomatXR "B" version module                 | 465           |

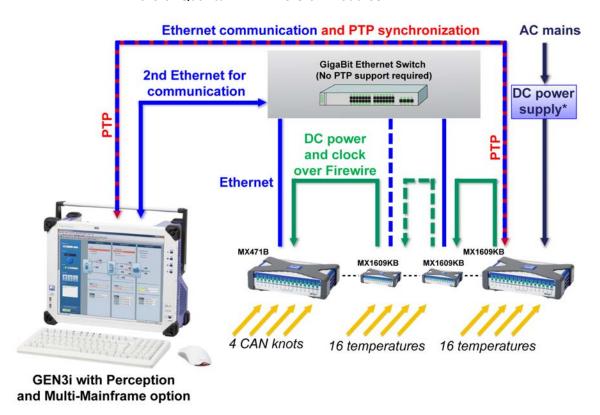

| F.3.3    | GEN3i/GEN3iA/GEN7i/GEN7iA with up to three QuantumX "B" version modules          | 466           |

| F.3.3.1  | Background network details                                                       | 467           |

| F.3.4    | GEN3i/GEN3iA/GEN7i/GEN7iA with standard network switch and four or more of Quant | tumX "B"      |

|          | version modules                                                                  | 467           |

| F.3.5    | GEN3i/GEN3iA/GEN7i/GEN7iA with PTP network switch and four or more of Quantum    | ( "B" version |

|          | modules                                                                          | 469           |

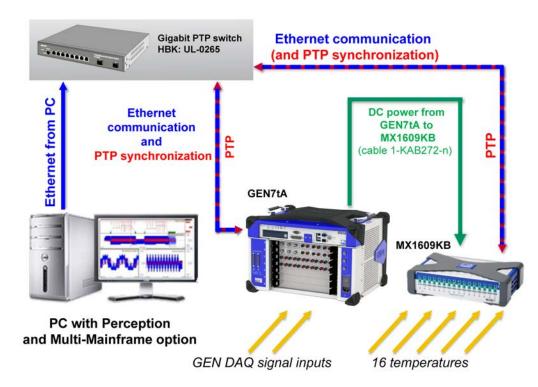

| F.3.6    | GEN7tA/GEN17tA with single QuantumX "B" version module                           | 470           |

| F.3.7    | GEN7tA with multiple QuantumX "B" version modules                                | 471           |

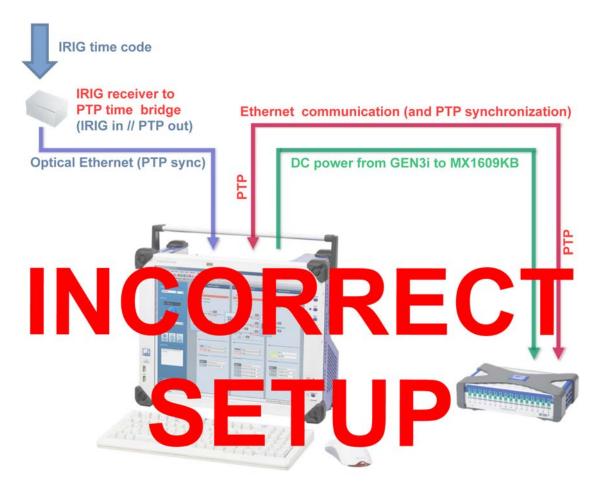

| F.3.8    | Genesis and QuantumX Setup using IRIG-to-PTP Bridge                              | 472           |

| F.3.9    | Genesis and QuantumX setup using GPS-to-PTP bridge                               | 473           |

| F.3.10   | Genesis using GPS-to-PTP bridge with Master/Sync Connected Systems               | 474           |

| F.3.11   | PTP Grandmasters                                                                 | 475           |

| F.3.11.1 | IRIG or GPS to PTP bridge                                                        | 475           |

| F.3.11.2 | GPS to PTP Bridge                                                                | 475           |

| F.3.11.3 | IRIG to PTP bridge                                                               | 475           |

| F.3.12   | HBK UL-0265 gigabit PTP switch                                                   | 476           |

| F.3.13   | Siemens Scalance XR234-12M PTP switch                                            | 477           |

| F.3.14   | PTP configuration errors                                                         | 478           |

| G        | Application Specific Usage                                                       | 479           |

| G.1      | Calculating maximum fiber cable length                                           | 479           |

| G 2      | Wake-on-LAN support (WOL)                                                        | 481           |

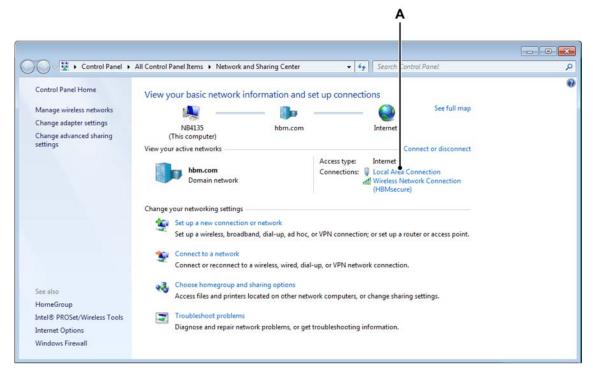

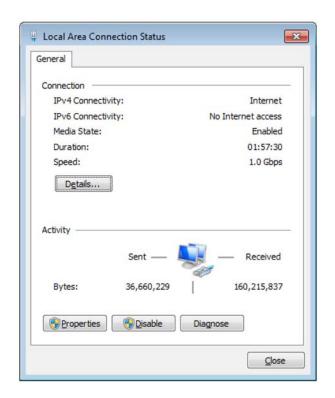

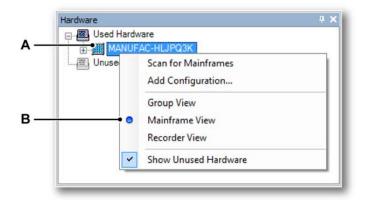

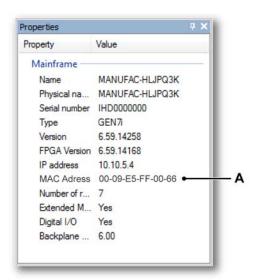

| G.2.1   | Locating GEN3i, GEN3iA, GEN7i and GEN7iA MAC/Physical address  |     |  |  |

|---------|----------------------------------------------------------------|-----|--|--|

| G.2.2   | Locating GEN3t, GEN7tA and GEN17tA MAC/Physical address        | 485 |  |  |

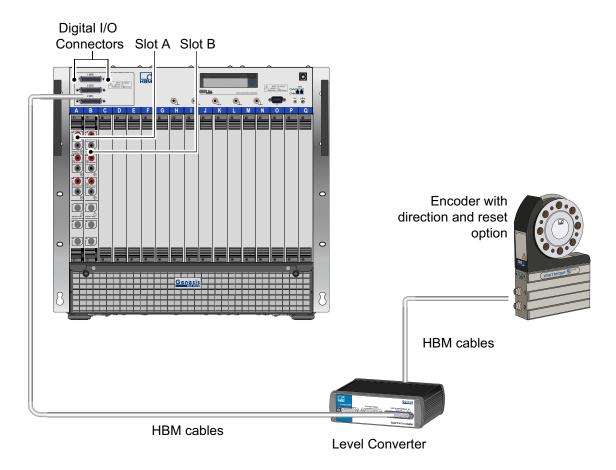

| G.3     | Configuring an encoder with direction and reset                | 487 |  |  |

| G.3.1   | From encoder to level converter                                | 488 |  |  |

| G.3.2   | From level converter to Digital I/O connector on the mainframe | 490 |  |  |

| G.3.3   | Activate Digital I/O channels with Perception                  | 490 |  |  |

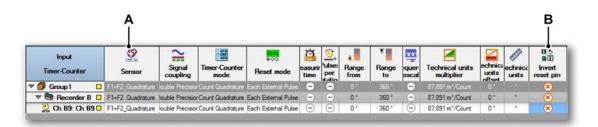

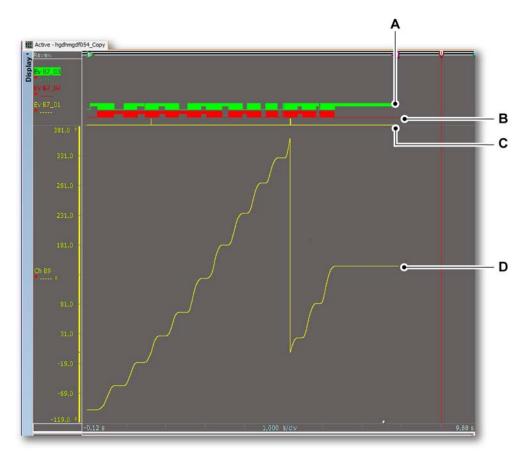

| G.3.3.1 | To activate Channel 8 or Channel 9 in Perception               | 493 |  |  |

| Н       | Disk Storage Technology                                        | 499 |  |  |

| H.1     | Most used RAID modes                                           | 499 |  |  |

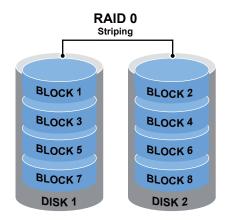

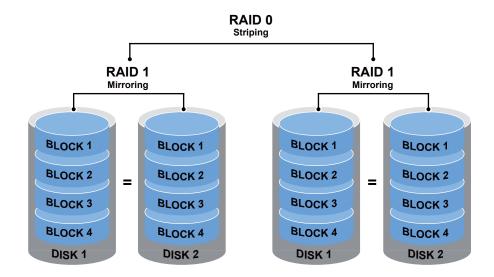

| H.1.1   | RAID 0 – Striping                                              | 501 |  |  |

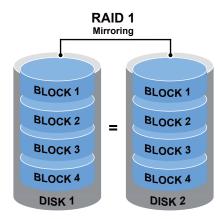

| H.1.2   | RAID 1 – Mirroring                                             | 502 |  |  |

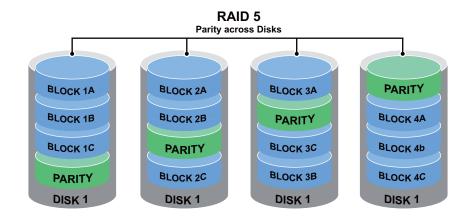

| H.1.3   | RAID 5 – Striping with parity                                  | 503 |  |  |

| H.1.4   | RAID level 10 – Combining RAID 0 & RAID 1                      | 504 |  |  |

## 1 About this manual

### 1.1 Symbols used in this manual

The following symbols are used throughout this manual to indicate warnings and cautions.

#### **WARNING**

Indicates a potentially hazardous situation which, if not avoided, could result in death or serious injury.

#### **WARNING**

Indicates an electrical shock hazard which, if not avoided, could result in death or serious injury.

#### **CAUTION**

Indicates a potentially hazardous situation which, if not avoided, could result in minor or moderate injury; or alerts against unsafe practices; or alerts against actions which could damage the product or result in a loss of data.

### **CAUTION**

The ESD susceptibility symbol indicates that handling or use of an item may result in damage from ESD if proper precautions are not taken.

## HINT/TIP

The info icon indicates sections which provide additional information about the product. This information is not essential for correct operation of the instrument, but provides knowledge to make better use of the instrument.

## 1.2 Manual conventions

When the wording "Click Start ..." is used, this refers to the Windows® Start button. Compared to Windows® XP, Windows® Vista, Windows® 7 and Windows® 10, the Start Menu has undergone some significant changes. The taskbar icon is no longer labeled "Start" and is now simply the pearl icon (of the window-frame in an orb).

For clarity and convenience, these conventions are used throughout this manual:

- Menu names from the display appear in bold, blue lettering.

- Settings within a menu appear in bold, red lettering.

- Front panel controls and control names appear in bold, black lettering.

## 2 Safety Messages

#### 2.1 Introduction

### **IMPORTANT**

### Read this section before using this product!

This instrument is mains powered and protective ground connections are required (unless otherwise specified for certain parts).

This manual contains information and warnings that must be observed to keep the instrument safe. The instrument should not be used when environmental conditions exceed the instrument's specifications (e.g. damp, high humidity) or if the unit is damaged.

For the correct and safe use of this instrument, it is essential that both operating and service personnel follow generally accepted safety procedures in addition to the safety precautions specified in this manual.

Whenever it is likely that safety protection has been impaired, the instrument must be made inoperative and secured against any unintended operation. Qualified maintenance or repair personnel should be informed. Safety protection is likely to be impaired if, for example, the instrument shows visible damage or fails to operate normally.

## Appropriate use

This instrument and the connected transducers may be used only for measurement and directly related control tasks. Any other use is not appropriate. To ensure safe operation, the instrument may only be used as specified in this user manual.

- The covers protect the user from live parts and should only be removed by suitably qualified personnel for maintenance and repair purposes.

- The instrument must not be operated with the covers removed.

- This instrument must not be used in life support roles.

- There are no user serviceable parts inside the instrument.

It is also essential to follow the respective legal and safety regulations for specific applications during use. The same applies to the use of accessories. Additional safety precautions must be taken in setups where malfunctions could cause major damage, loss of data or even personal injury.

Some examples of precautions are: mechanical interlocking, error signaling, limit value switches, etc.

#### Maintenance and cleaning

The instrument is a maintenance-free product. However, please note the following information about cleaning the housing:

- Before cleaning, disconnect the instrument completely.

- Clean the housing with a soft, slightly damp (not wet!) cloth. Never use solvents, since these could damage the housing or the labeling on the front panel.

- When cleaning, ensure that no liquid gets into the housing or connections.

### General dangers, failing to follow the safety instructions

This instrument is a state-of-the-art device and as such is fail-safe. Using this instrument may be hazardous if it has been installed incorrectly and is operated by untrained personnel. Any person assigned to install, maintain or repair the unit or to put the unit into operation must have first read and understood the user manual, particularly the technical safety instructions.

#### Residual risks

This instrument's scope of supply and performance covers only a small area of measurement technology. In addition, equipment planners, installers and operators should plan, implement and respond to the safety engineering considerations of measurement technology in such a way as to minimize any residual risks. Prevailing regulations must be complied with at all times. The residual risks of the measurement technology must be referenced.

## **Conversions and modifications**

Neither the design nor the safety features of this instrument may be modified without our express prior written agreement. Any modification shall exclude all liability on our part for any resultant damage. In particular, any repair or soldering work on cards (replacement of components) is prohibited. When exchanging complete units, use only original parts from HBM. The unit is delivered from the factory with a fixed hardware and/or software configuration. Changes should only be made within the possibilities documented in this manual.

#### Qualified personnel

People entrusted with the installation, fitting, operation of the instrument and putting the unit into service must have the appropriate qualifications. The instrument may only be installed and used by qualified personnel, in strict accordance with the specifications and the safety rules and regulations. This includes people who meet at least one of the three following qualification levels:

- Project personnel: Have a working knowledge of the safety concepts of automation and test and measurement technology.

- Automation plant or test and measurement operating personnel: Have been instructed on how to handle the equipment and are familiar with the operation of the cards and technologies described in this documentation.

- Commissioning engineers or service engineers: Have successfully completed the training on how to repair the automation systems. They are also authorized to activate, to ground and to label circuits and equipment in accordance with engineering safety standards. It is essential that the legal and safety requirements for the product and any accessories are complied with during use.

## 2.2 Grounding

The instrument must be used with a protective ground connection via the protective ground conductor of the supply cable. The protective ground conductor is connected to the instrument before the line and neutral connections are made when the supply connection is made. If the final connection to the supply is made elsewhere, ensure that the ground connection is made before line and neutral connections are made.

#### **WARNING**

Any interruption of the ground connection, inside or outside the instrument, is likely to make the instrument dangerous. Intentional interruption is prohibited.

For protection against electric shock, all external circuits or equipment need a safe insulation. Therefore, peripheral equipment must not be connected to the system with a power supply without the SELV (Separated Extra Low Voltage) rating unless explicitly mentioned.

Signal connections to the instrument should be connected after the ground connection is made and disconnected before the ground connection is removed, i.e. the supply lead must be connected whenever signal leads are connected.

### **WARNING**

For safety, it is essential that the protective ground connector of the instrument is used whenever voltages greater than 33 V RMS, 46.7 V PEAK or 70 V DC (IEC 61010-1:2010) are connected. This is to prevent the instrument's case becoming live in the event of a protective ground interruption, which could occur if the supply connector is accidentally disconnected from the instrument.

The primary purpose of protective grounding is to provide adequate protection against electric shock that could cause death or injury to personnel while working on de-energized equipment. This is accomplished by grounding and bonding to limit the body contact or exposure to voltages at the work-site to a safe value if the equipment were to be accidentally energized from any source of hazardous energy. The greatest source of hazardous energy in most cases is direct energizing of the equipment from a power-system or source.

## **WARNING**

If connection to a protective ground is not possible for any reason, then please refer to the international safety standard EN 50191:2000

## 2.2.1 Mains power cord

### **WARNING**

Do not use the equipment with damaged cords and/or cables. Replace a damaged cord and/or cable immediately.

## 2.3 Instrument symbols

A variety of symbols can be found in the system. Below is a list of symbols and their meaning.

This symbol is used to denote the measurement ground connection. This point is not a protective ground connection.

This symbol is used to denote a protective ground connection.

This symbol is used to denote a frame or chassis ground connection. This point is not a protective ground connection.

Where caution is required, this symbol refers to the user manual for further information.

This symbol warns that high voltages are present close to this symbol.

This symbol shows that the switch is a power switch. When pressed, the instrument state toggles between the operating and power-off mode. When the system is in power-off mode, all electronics are disconnected from the power, except for a small circuit used to detect the switch state.

#### 2.4 Protection and isolation

## 2.4.1 Measurement categories

- The international standards for test equipment safety are IEC 61010-1 and the IEC 61010-2-030.

- IEC 61010-1 defines three overvoltage categories (CAT II, CAT III, and CAT IV) for the power supply of an instrument.

- IEC 61010-2-030 defines three measurement categories (CAT II, CAT III, and CAT IV) for an instrument's input measurements which can be directly connected to mains supply.

- All measurement inputs which are not specified to be connected to the mains power have no CAT rating and are referred to as O (like Others).

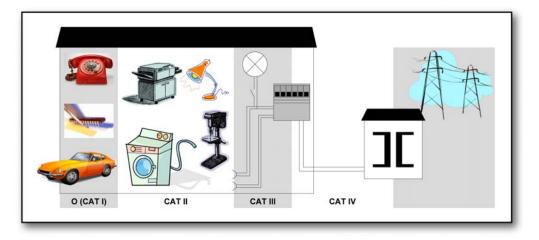

### Categories in accordance with IEC 61010-2-030:2010

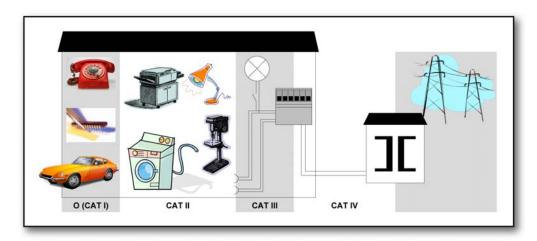

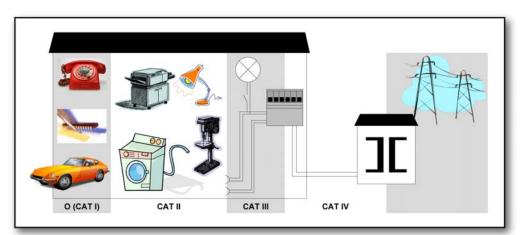

Electrical equipment, specifically measurement tools, can be assigned into four categories in accordance with IEC 61010-2-030:2010. These measurement categories are indicated by the terms O (previously CAT I), CAT II, CAT III and CAT IV. Originally, these categories were used to indicate the overvoltage or surge voltage that was likely to occur and could be sustained by the equipment. Currently, the category indicates the amount of energy that can be released if a short circuit occurs. A higher category number indicates a higher energy level that can occur and can be sustained by the equipment.

**O** (Other) (previously referred to as **CAT I**): This category is for measurements not directly connected to a mains supply. Measurements for this category are signal levels, regulated low voltage circuits or protected secondary circuits. For this category, there are no defined standard overvoltage or surge impulse levels.

**CAT II**: This category is for measurements directly connected to a low voltage mains supply. Measurements for this category are mains sockets in household applications or portable tools. This category expects a minimum of three levels of overcurrent protection between the transformer and connection point of the measurement. (See Figure 2.1).

**CAT III**: This category is for measurements directly connected to the distribution part of a low voltage mains installation. Measurements for this category are circuit breakers, wiring, junction boxes, etc. This category expects a minimum of two levels of overcurrent protection between the transformer and connection point of the measurement. (See Figure 2.1).

**CAT IV**: This category is for measurements directly connected to the source of a low voltage mains installation. Measurements for this category are overcurrent protection devices, ripple control units, etc. This category expects that there is a minimum of one level of overcurrent protection between the transformer and connection point of the measurement circuit. (See Figure 2.1).

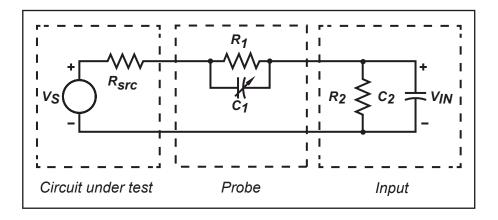

Figure 2.1: Category indication in accordance with IEC 61010-2-030:2010

**Example:** A measurement device is specified as 600 V CAT II, maximum input voltage 1000 V DC.

Table 2.1: Insulation test voltages in accordance with IEC 61010-2-030:2010

| Nominal Voltage<br>(V RMS or V DC) | IEC 61010-2-030:2010   |         |        |                  |         |        |

|------------------------------------|------------------------|---------|--------|------------------|---------|--------|

|                                    | 5 sec. AC test (V RMS) |         |        | Impulse test (V) |         |        |

|                                    | CAT II                 | CAT III | CAT IV | CAT II           | CAT III | CAT IV |

| ≤ 150                              | 840                    | 1390    | 2210   | 1550             | 2500    | 4000   |

| > 150 ≤ 300                        | 1390                   | 2210    | 3310   | 2500             | 4000    | 6000   |

| > 300 ≤ 600                        | 2210                   | 3310    | 4260   | 4000             | 6000    | 8000   |

| > 600 ≤ 1 000                      | 3310                   | 4260    | 6600   | 6000             | 8000    | 12000  |

Using the table above, it can be concluded that this specification informs the user that the device passed the insulation tests; 5 sec at 2210 V RMS and impulse 4000 V. The maximum operating input voltage is 1000 V DC. This device is to be used to measure CAT II circuitry up to 600 V.

### **WARNING**

Measurement inputs of this instrument should not be used to measure high-energy signals of measurement categories CAT II, CAT III or CAT IV (IEC 61010-2-030:2010) (e.g. mains measurements), unless specifically stated for the specific input.

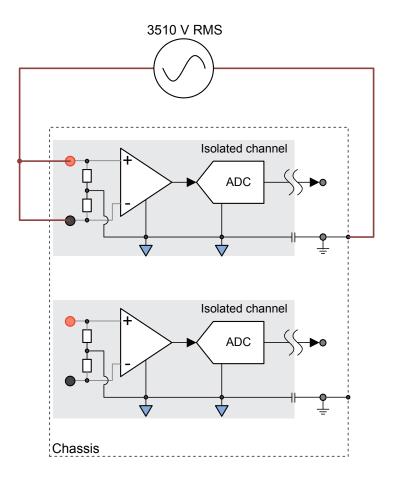

### 2.4.2 Basic insulation versus reinforced

For reference, the basic insulation and supplementary insulation and the reinforced insulation test values for CAT II can be found below.

Table 2.2: Test voltages for the testing electric strength of solid insulation in measuring circuits in measurement category II (IEC 61010-2-030:2010)

| Nominal<br>voltage line to<br>neutral AC<br>RMS or DC of<br>MAINS being<br>measured. [V] | Test voltage                                  |      |                                                        |                       |

|------------------------------------------------------------------------------------------|-----------------------------------------------|------|--------------------------------------------------------|-----------------------|

|                                                                                          | 5 s AC test [V RMS]                           |      | Impulse test [V peak]                                  |                       |

|                                                                                          | Basic insulation and supplementary insulation |      | Basic<br>insulation and<br>supplementary<br>insulation | Reinforced insulation |

| ≤ 150                                                                                    | 840                                           | 1390 | 1550                                                   | 2500                  |

| > 150 ≤ 300                                                                              | 1390                                          | 2210 | 2500                                                   | 4000                  |

| > 300 ≤ 600                                                                              | 2210                                          | 3510 | 4000                                                   | 6400                  |

| > 600 ≤ 1000                                                                             | 3310                                          | 5400 | 6000                                                   | 9600                  |

Several means of protection can be used to protect a user from hazardous voltages. As can be seen below, basic insulation and supplementary insulation is one mean of protection, but reinforced insulation is also a means of protection.

The test voltages are different for each mean of protection, as can be found in the table above.

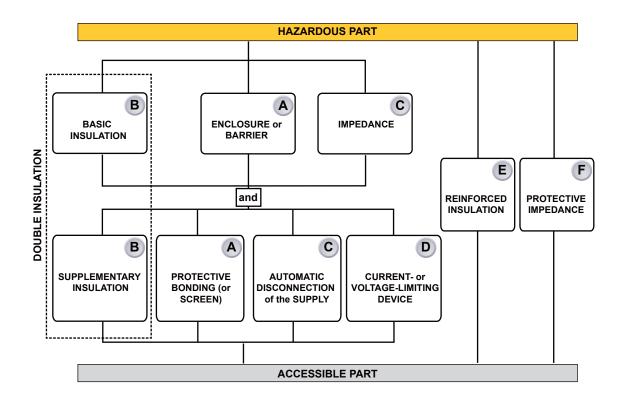

#### Additional means of protection for single fault conditions

Accessible parts shall be prevented from becoming HAZARDOUS LIVE IN SINGLE FAULT CONDITION. The primary means of protection (see Figure 2.2) shall be supplemented by one of **A**, **B**, **C** or **D**. Alternatively, one of the single means of protection **E** or **F** shall be used. See Figure 2.2.

Figure 2.2: Acceptable arrangement of protective means against electric shock

Example: A measurement device is specified as 600 V CAT II reinforced insulation, with a maximum input voltage 1000 V DC.

Using the information above, it can be concluded that this specification informs the user that the measurement device is tested on input to chassis ground for five seconds at 3510 V RMS and impulse 6400 V. The maximum operating input voltage is 1000 V DC. This device is to be used to measure CAT II circuitry up to 600 V.

## 2.4.3

## Protection WARNING

#### **ELECTRICAL SHOCK HAZARD!**

Any interruption of the protective conductor inside or outside the apparatus is likely to make the apparatus dangerous. Intentional interruption is prohibited.

When the apparatus is connected to its supply, terminals may be live, and the opening of covers for removal of parts is likely to expose live parts.

Whenever it is likely that the protection has been impaired, the apparatus must be made inoperative and be secured against any unintended operation.

The protection is likely to be impaired if, for example, the apparatus shows visible damage or has been subjected to severe transport stresses.

It is the responsibility of the user to ensure the safety of any accessories used with the equipment, such as probes.

Proper use of this device depends on careful reading of all instructions and labels.

If the instrument is used in a manner not specified by HBM, the protection provided by the instrument can be impaired.

### **WARNING**

This instrument must not be operated in explosive atmospheres.

### **WARNING**

This instrument and related accessories are not designed for biomedical experimentation on humans or animals and should not be directly connected to human or animal subjects or used for patient monitoring.

### 2.4.4 Overvoltage/current protection

All signal inputs are protected against overloads and transients. Exceeding the limits stated in the specifications, particularly when connected to potentially high-energy sources, can cause severe damage that is not covered by the manufacturer's warranty.

#### **WARNING**

Do not remove covers. Refer to qualified individuals for servicing.

The covers protect the user from live parts and should only be removed by suitably qualified personnel for maintenance and repair purposes.

The instrument must not be operated with the covers removed.

There are no user serviceable parts inside.

## 2.4.5

# Isolation CAUTION

For input channels with plastic BNCs (galvanically isolated from the chassis), the input conductors including the BNC shell may carry hazardous voltages. Only appropriate insulated BNC connectors should be used.

It is the responsibility of the user to ensure the safety of any accessories used with the instrument, such as probes.

#### **CAUTION**

Even low voltage inputs may contain high voltage fast transients (spikes), which could damage the input. For this reason it is not safe, for instance, to make direct connections to an AC line supply, unless specifically stated otherwise for the specific input.

#### 2.5 Environment

The instrument should be operated in a clean, dry environment with an ambient temperature as specified in the data sheets.

The instrument is specified for use in a Pollution Degree II environment, which is normally non-conductive with temporary light condensation, but it must not be operated while condensation is present. It should not be used in more hostile, dusty or wet conditions, as specified in the Pollution Degree II environment.

Humidity should be between 0% and 80%. When moving the device from a cold to a warm environment, the device has to be left off for a period of 30 minutes to avoid short circuits as a result of condensation.

**Note** Direct sunlight, radiators and other heat sources should be taken into account when assessing the ambient temperature.

If the instrument has a fan installed, leave space around the equipment for unrestricted ventilation.

Do not store the equipment in hot areas. High temperatures can shorten the life of electronic devices and damage batteries.

Do not store the equipment in cold areas. Before the equipment warms up to its normal operating temperature, moisture can form inside the equipment, which may damage the equipment's electronic circuits.

Do not drop, knock or shake the equipment. Rough handling can break internal electronics and/or PCBs.

Do not use harsh chemicals, cleaning solvents or strong detergents to clean the instrument. To clean the instrument, disconnect all power sources and clean the housing with a soft, slightly damped (not wet!) cloth.

It is the responsibility of the user to ensure the safety of any accessories used with the instrument, such as probes.

## 2.6 Laser Safety

Some of the GEN series cards or systems use lasers. All laser products used are classified as a **Class 1 laser product**. The lasers do not emit hazardous light but it is recommended to avoid direct exposure to the beam.

#### **WARNING**

Intrabeam viewing of the laser product may produce dazzling visual effects, particularly in low ambient light. Lasers of any wavelength with sufficient output power can cause injury.

The built-in laser complies with laser product standards set by government agencies for Class 1 laser products:

The GEN series products are certified as Class 1 Laser Products and comply with US FDA regulations. These are certified by TÜV and CSA to meet the Class 1 eye safety requirements of EN (IEC) 60825 and the electrical safety requirements of EN (IEC) 60950. The devices are for use only under the specifications and ratings specified in the manual and data sheets.

### **CAUTION**

Use of controls or adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

## 2.7 Manual handling of loads

The Manual Handling of Loads Directive 90/269/EEC from the European Community lays down the minimum health and safety requirements for the manual handling of loads where there is a risk particularly of back injury to workers.

#### **CAUTION**

The weight of the instrument may exceed 17.5 kg when fully loaded. Please take appropriate actions before lifting the instrument.

Before lifting or carrying a heavy object, the following questions should be asked:

- Can one person lift this load safely, or do two people need to lift the load?

- How far will the load have to be carried?

- Is the path clear of clutter, cords, slippery areas, overhangs, stairs, curbs or uneven surfaces?

- Will closed doors that need to be opened be encountered?

- Once the load is lifted, will it block the carrier's view?

- Can the load be broken down into smaller parts?

- Should the carrier wear gloves to get a better grip and to protect hands?

Contact the "Occupational Health and Safety" organization, or equivalent, in your country for more information.

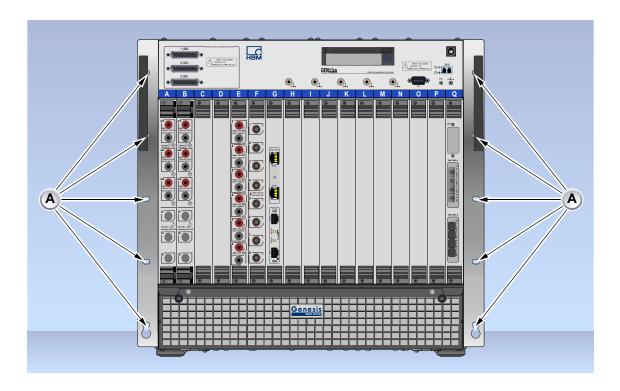

The GEN17tA weighs approximately 35.9 kg with 17 acquisition cards plugged in (18.9 kg without acquisition cards)

## 2.8 International safety warnings

Dansk

#### **SIKKERHEDSADVARSEL**

Dette instrument skal anvendes med en sikkerhedsjordforbindelse, som er tilsluttet via lysnetkablets beskyttelsesjordledning eller via en sikkerhedsjordklemme, hvis instrumentet er forsynet hermed. Hvis sikkerhedsjordforbindelsen afbrydes, inden i eller uden for instrumentet, kan instrumentet udgøre en farekilde. Sikkerhedsjordforbindelsen må ikke afbrydes. Der skal desuden tilsluttet en signaljordforbindelse, hvis et indgangssignal overstiger 33 V RMS, 46,7 V PEAK eller 70 V DC (IEC 61010-1:2010).

Dækslerne må ikke fjernes.

Afbryd dette instrument eller dets strømforsyning fra lysnettet ved at fjerne IEC-stikket. Instrumentets vekselstrømsafbryder er kun beregnet til funktionelle formål. Den er ikke beregnet eller egnet til at afbryde instrumentet fra lysnettet.

Hvis målingerne et omfattet af EN 50110-1 og EN 50110-2, skal alle kort med en driftsspænding på mere end 50 V AC RMS eller 120 V DC tilsluttes af en kvalificeret tekniker eller en elektriker, og arbejdet skal kontrolleres af en kvalificeret tekniker. (En kvalificeret tekniker er en person, som i kraft af sin specialuddannelse, sin viden og erfaring samt sit kendskab til relevante bestemmelser kan vurdere omfanget af det arbejde, de skal udføre, og afdække de potentielle risici, og som er blevet udpeget som kvalificeret tekniker af deres arbejdsgiver).

#### VEILIGHEIDSWAARSCHUWING

Dit instrument mag uitsluitend worden gebruikt als een beschermde massa (aarde) is aangesloten via de beschermde massageleider van de voedingskabel, of indien het instrument daarvan is voorzien via de veiligheidsmassa-aansluiting. Als de beschermde massa, binnen of buiten het instrument, wordt onderbroken, dan kan dat hierdoor uitermate gevaarlijk worden. Het opzettelijk onderbreken van de massa is verboden. Indien er een signaal wordt aangeboden van meer dan 33 V RMS, 46.7 Vpeak of 70 V DC (IEC 61010-1:2010) dient eveneens een signaalaarding aangesloten te zijn.

De deksels mogen nooit worden verwijderd.

Om dit instrument los te koppelen of van het stroom af te halen, dient de IECaansluiting er uit te worden getrokken. De wisselstroom-voedingsschakelaar op dit instrument is uitsluitend bestemd voor functionele doeleinden. Het is niet bedoeld of geschikt als een ontkoppelingsapparaat.

Voor metingen die binnen de EN 50110-1 en EN 50110-2 vallen: let op dat alle panelen met bedrijfsspanningen van meer dan 50 V AC RMS of 120 V DC alleen door een gekwalificeerde technicus mogen worden aangesloten of door een persoon die is opgeleid in de elektrotechniek en onder toezicht van een gekwalificeerde technicus staat. (Gekwalificeerde technici zijn personen, die op basis van hun specialistische opleiding, kennis en ervaring als ook hun kennis van de betreffende voorzieningen, in staat zijn om het werk dat aan hen is toevertrouwd te beoordelen en mogelijke gevaren te ontdekken en door hun werkgever zijn aangewezen als gekwalificeerde technici.)

A04377\_03\_E00\_00 HBK: UNRESTRICTED

#### **TURVAOHJEITA**

Tätä laitetta käytettäessä sen tulee olla suojamaadoitettu joko verkkojohdon suojajohtimen tai erillisen suojamaadoitusliitännän kautta, mikäli laitteeseen on sellainen asennettu. Suojamaadoituksen katkaiseminen laitteen sisä- tai ulkopuolelta tekevät siitä vaarallisen. Tahallinen katkaisu on kiellettyä. Lisäksi signaalimaa on oltava kytkettynä, jos jokin tulosignaali ylittää tehollisarvon 33 V, huippuarvon 46,7 V tai 70 V DC (IEC 61010-1:2010).

Älä poista suojakansia.

Katkaise laitteen tai sen virtalähteen käyttöjännite irrottamalla IEC-liitin. Laitteen verkkokytkimellä on ainoastaan toiminnallinen tarkoitus. Sitä ei ole tarkoitettu, eikä se sovellu laitteen erottamiseen käyttöjännitteestä.

Mittauksissa, jotka kuuluvat EN 50110-1- ja EN 50110-2-standardien soveltamisalaan, huomaa, että kortit, jotka toimivat tehollisarvojännitteellä yli 50 V AC tai 120 V DC, saa kytkeä vain pätevä asentaja tai sähköteknisen koulutuksen saanut henkilö pätevän asentajan valvonnassa. (Pätevät asentajat ovat henkilöitä, jotka erikoiskoulutuksensa, tietojensa ja kokemuksensa sekä asiaan kuuluvien määräysten tuntemuksensa ansiosta pystyvät arvioimaan heille annettuja töitä ja havaitsemaan mahdolliset vaarat ja jotka heidän työnantajansa on nimennyt ammattitaitoisiksi asentajiksi).

#### **ATTENTION - DANGER!**

Lorsqu'il est en fonctionnement, cet instrument doit impérativement être mis à la masse par le conducteur de terre du câble d'alimentation ou, si l'instrument en comporte une, par la borne de terre. Il peut être dangereux en cas de coupure du circuit de terre, que ce soit à l'intérieur ou à l'extérieur de l'instrument. Il est formellement interdit de couper intentionnellement le circuit de terre. De plus, une masse signal doit être connectée si l'un des signaux d'entrée, quel qu'il soit, dépasse 33 V RMS (valeur efficace), 46,7 V PEAK (valeur de crête) ou 70 V DC (courant continu) (CEI 61010-1:2010).

Ne pas déposer les panneaux de protection.

Pour déconnecter cet instrument ou son alimentation de l'alimentation secteur, débrancher le cordon d'alimentation (CEI). L'interrupteur d'alimentation secteur sur cet instrument est purement fonctionnel. Il ne s'agit pas d'un dispositif de coupure du courant, et n'est pas conçu pour cette fonction.

Pour les mesures entrant dans le champ d'application des normes EN 50110-1 et EN 50110-2, veuillez noter que tous les panneaux avec des tensions de service supérieures à 50 V AC RMS (tension efficace) ou 120 V DC (courant continu) ne peuvent être connectés que par un technicien qualifié ou une personne formée en ingénierie électrique et supervisée par un technicien qualifié. (Les techniciens qualifiés sont des personnes qui, du fait de leur formation, leurs connaissances et leur expérience spécialisées ainsi que leur connaissance des dispositions réglementaires appropriées, sont capables d'évaluer le travail qui leur est confié et détecter les risques possibles, et qui ont été désignées comme techniciens qualifiés par leur employeur).

#### **WARNHINWEIS!**

Dieses Gerät muss mit einer Schutzerde betrieben werden, die über den Schutzleiter des Speisekabels oder über die Erdungsklemme des Gerätes (falls vorhanden) anzuschließen ist. Bei einer Unterbrechung der Schutzerde außerhalb oder innerhalb des Gerätes kann eine Gefahr am Gerät entstehen. Eine beabsichtigte Unterbrechung ist nicht zulässig. Achtung! Bei Signalspannungen über 33 V Effektivwert, 46,7 V Spitzenwert oder 70 V Gleichspannung (IEC 61010-1:2010) muss die Signalmasse angeschlossen sein.

Die Schutzabdeckungen nicht entfernen.

Zum Trennen des Gerätes oder seiner Spannungsversorgung von der Wechselstromversorgung den IEC-Stecker abziehen. Der Wechselstromversorgungs-Schalter dient bei diesem Gerät nur für Funktionszwecke. Er ist nicht als Trennvorrichtung bestimmt bzw. geeignet.

Für Messungen gemäß EN 50110-1 und EN 50110-2 bitte berücksichtigen, dass alle Platinen mit Betriebsspannungen über 50 V AC RMS oder 120 V DC nur durch einen qualifizierten Elektriker oder einer elektrotechnisch unterwiesenen Person unter Aufsicht eines qualifizierten Technikers durchgeführt werden dürfen. (Qualifizierte Techniker sind aufgrund ihrer fachlichen Ausbildung, Kenntnisse und Erfahrungen sowie Kenntnis der einschlägigen Bestimmungen in der Lage, die ihnen anvertrauten Arbeiten zu beurteilen und mögliche Risiken zu erkennen, sowie Personen, die durch ihren Arbeitgeber zu qualifizierten Technikern ernannt worden sind).

#### **AVVISO DI SICUREZZA**

Questo strumento deve esser utilizzato con un collegamento protettivo di messa a terra tramite il filo di messa a terra del cavo di alimentazione o tramite il terminale di messa a terra in sicurezza, nel caso in cui lo strumento ne sia dotato. Qualsiasi interruzione della messa a terra di protezione, sia all'interno che all'esterno dello strumento, lo renderà pericoloso. È vietata qualsiasi interruzione causata intenzionalmente. Inoltre, la connessione di terra deve essere collegata se ad uno qualsiasi degli ingressi viene applicato un segnale superiore a 33 V RMS, 46,7 V di picco o 70 V c.c. (IEC 61010-1:2010).

Non rimuovere le coperture.

Per disinnestare questo strumento o l'alimentazione dalla corrente alternata, scollegare il connettore IEC. L'interruttore dell'alimentazione a corrente alternata di questo strumento viene fornito esclusivamente per scopi operativi e non viene inteso, né è adatto, per essere utilizzato come dispositivo di disinnesto.

Si noti che per le misurazioni che rientrano nell'ambito di applicazione delle norme EN 50110-1 ed EN 50110-2, tutte le schede con tensioni di esercizio superiori a 50 V c.a. RMS o 120 V c.c. possono essere collegate esclusivamente da un tecnico qualificato o da una persona in possesso di una formazione specifica nel campo dell'ingegneria elettrica sotto la supervisione di un tecnico qualificato. (Per tecnico qualificato si intende una persona che, in virtù della propria formazione , preparazione ed esperienza specialistica, nonché conoscenza delle disposizioni di settore, è in grado di valutare il lavoro che gli viene assegnato e di individuare possibili rischi, oltre ad essere stato nominato tecnico qualificato dal proprio datore di lavoro).

#### **ADVARSEL!**

Dette instrument må betjenes med beskyttelsesjord tilkoblet via beskyttelsesjordlederen til tilførselskabelen eller via beskyttelsesjordklemmen, hvis instrumentet er utstyrt med en slik. Ethvert brudd i beskyttelsesjorden inni eller utenpå instrumentet kan føre til at instrumentet blir farlig. Tiltenkt brudd er tillatt. I tillegg må en signaljord tilkobles hvis et inngangssignal overskrider 33 V RMS, 46,7 V PEAK eller 70 V DC (IEC 61010-1:2010).

Ikke fjern dekslene.

For å koble dette instrumentet eller dets strømforsyning fra AC-tilførselen, trekker du ut IEC-kontakten. AC-tilførselsbryteren på dette instrumentet er kun for funksjonelle formål. Den er ikke beregnet for, eller egnet til frakoblingsenhet.

For målinger som faller innenfor EN 50110-1 og EN 50110-2 må man være oppmerksom på at alle kort med arbeidsspenninger over 50 V AC RMS eller 120 V DC kun kan kobles til av en kvalifisert tekniker eller elektriker og overvåket av en kvalifisert tekniker. (Kvalifiserte teknikere er personer som på grunn av sin spesialistopplæring, kunnskap og erfaring, samt sin kunnskap om relevante bestemmelser, er i stand til å gå inn i arbeidet som de har fått i oppdrag å utføre og detektere mulige farer, og som er blitt utnevnt som kvalifiserte teknikere av sin arbeidsgiver.

#### **AVISO DE SEGURANÇA**

Este instrumento deve funcionar com uma terra de proteção conectada através do condutor da terra de proteção do cabo de alimentação ou, caso o instrumento esteja equipado com um, através do terminal da terra de proteção. Qualquer interrupção da terra de proteção, no interior ou no exterior do instrumento, poderá tornar o instrumento perigoso. A interrupção intencional é proibida. Além disso, deve ser conectado um sinal de terra se qualquer sinal de entrada exceder 33 V RMS, 46,7 V PICO ou 70 V CC (IEC 61010-1:2010).

Não retirar as tampas.

Para desconectar este instrumento ou a respetiva fonte de alimentação da alimentação CA, retire o conector IEC da ficha. Neste instrumento, o interruptor de alimentação CA é fornecido apenas para fins funcionais. Não se destina a, nem é adequado para, ser utilizado como dispositivo de desconexão.

Para medições abrangidas pelas normas EN 50110-1 e EN 50110-2, tenha em atenção que todos os quadros com tensões de funcionamento superiores a 50 V CA RMS ou 120 V CC apenas poderão ser conectados por um técnico qualificado ou por alguém com formação em engenharia elétrica e supervisionados por um técnico qualificado. (Técnicos qualificados são pessoas que, devido à sua formação especializada, ao conhecimento e à experiência, bem como ao seu conhecimento das disposições relevantes, são capazes de avaliar o trabalho que lhes é confiado e detetar possíveis riscos e são pessoas que foram nomeadas técnicos qualificados pelo seu empregador.)

#### **AVISO DE SEGURANÇA**

Este instrumento deve ser operado com um terra de proteção conectado por meio do condutor do terra de proteção do cabo de alimentação ou, se o instrumento estiver equipado com um, por meio do terminal de aterramento de segurança. Qualquer interrupção do terra de proteção, no interior ou no exterior do instrumento, poderá tornar o instrumento perigoso. A interrupção intencional é proibida. Além disso, deve ser conectado um sinal de terra se qualquer sinal de entrada exceder um máximo de 33 V RMS, 46,7 V PICO ou 70 V CC (IEC 61010-1:2010).

Não retirar as tampas.

Para desconectar este instrumento ou a fonte de alimentação dele da alimentação CA, desconecte o conector IEC. Neste instrumento, o interruptor de alimentação CA é fornecido somente para fins funcionais. Não se destina a, nem é adequado para, ser usado como dispositivo de desconexão.

Para medições no escopo das normas EN 50110-1 e EN 50110-2, note que todos os quadros com tensões de funcionamento superiores a 50 V CA RMS ou 120 V CC poderão somente ser conectados por um técnico qualificado ou por alguém com formação em engenharia elétrica e supervisionados por um técnico qualificado. (Os técnicos qualificados são pessoas que, devido à sua formação acadêmica, conhecimento e experiência, bem como ao seu conhecimento das provisões relevantes, são capazes de avaliar o trabalho que lhes é confiado e detectar possíveis riscos e são pessoas que foram nomeadas técnicos qualificados por seu empregador.)

#### ADVERTENCIA SOBRE SEGURIDAD

Este instrumento debe utilizarse conectado a tierra a través del conductor de puesta a tierra del cable de alimentación o de la borna de seguridad, si dicho instrumento estuviera equipado con ella. Cualquier interrupción de esta puesta a tierra, dentro o fuera del instrumento, hará que el manejo del mismo resulte peligroso. Queda terminantemente prohibido dejar en circuito abierto dicha puesta a tierra. Además, debe conectarse una señal de tierra si cualquier señal de entrada sobrepasa los 33 V eficaces, los 46,7 V de PICO o los 70 V de CC (IEC 61010-1:2010).

No quite las tapas.

Para desconectar este instrumento o su fuente de alimentación de la CA, desenchufe el conector IEC. El interruptor de entrada de CA (encendido) se incluye solo para fines funcionales. No está pensado para utilizarse como medio de desconexión, ni tampoco es adecuado para ello.

En cuanto a las mediciones que se clasifiquen bajo el alcance de las normas EN 50110-1 y EN 50110-2, tenga en cuenta que los cuadros con tensión de funcionamiento por encima de los 50 V de CA eficaces o los 120 V de CC solo puede conectarlos un técnico cualificado o una persona con formación en ingeniería eléctrica y supervisada por un técnico cualificado. (Los técnicos cualificados son personas que, debido a su formación especializada, conocimientos y experiencia, así como por su conocimiento de los suministros pertinentes, son capaces de evaluar el trabajo encomendado y detectar posibles riesgos, al igual que personas nombradas como técnicos cualificados por la empresa contratadora).

#### **SÄKERHETSVARNING**

Detta instrument måste användas med jordad anslutning via strömkabelns ledare eller, om sådan finns, via en isolerad jordterminal. Avbrott i den isolerande jordningen inuti eller utanför strömgivaren kan göra strömgivaren farlig. Avsiktligt avbrott är förbjudet. Dessutom måste en signaljordning anslutas om någon ingångssignal överskrider 33 V RMS, 46.7 V PEAK eller 70 V DC (IEC 61010-1:2010).

Ta inte bort skydden.

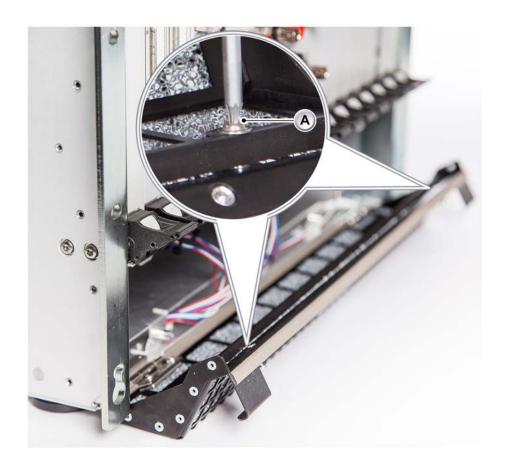

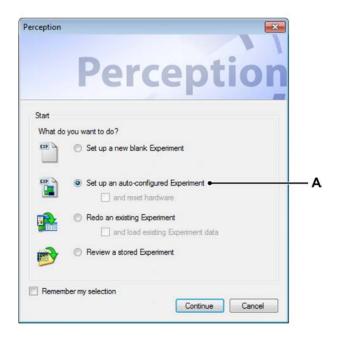

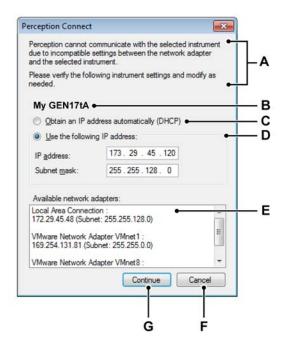

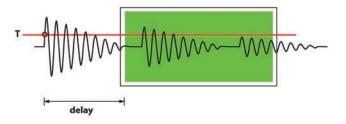

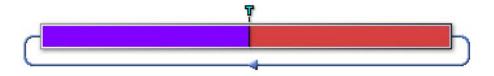

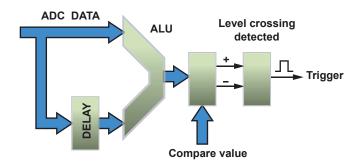

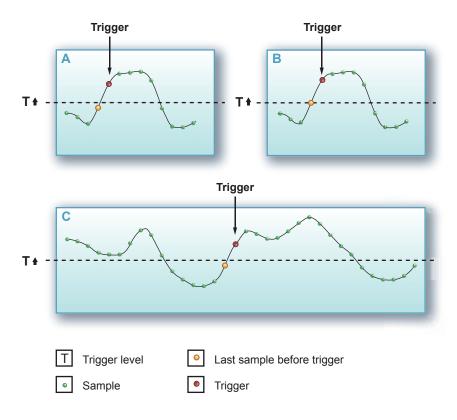

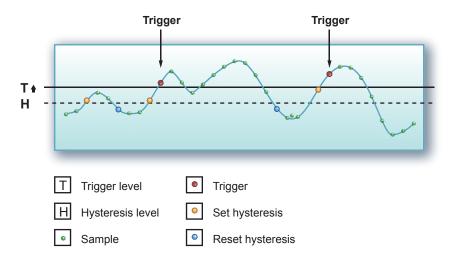

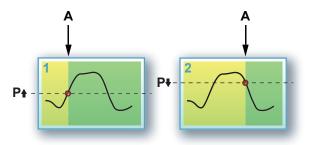

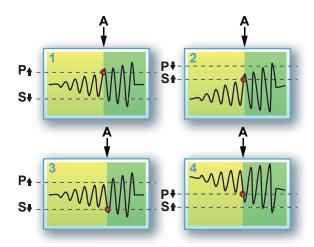

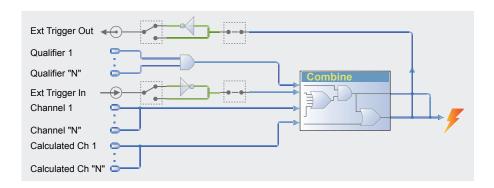

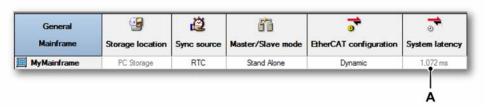

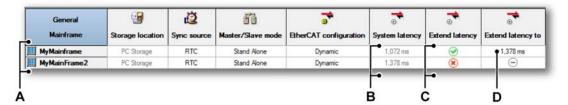

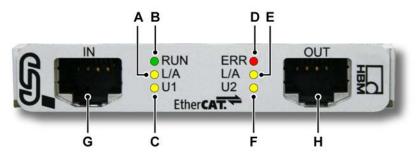

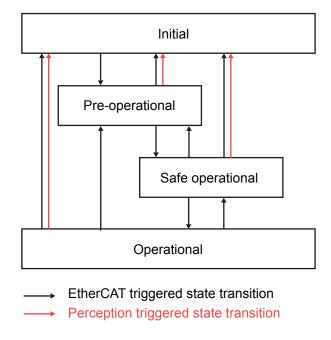

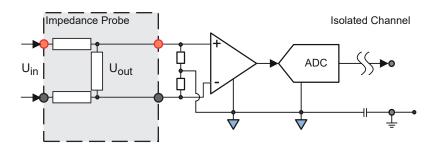

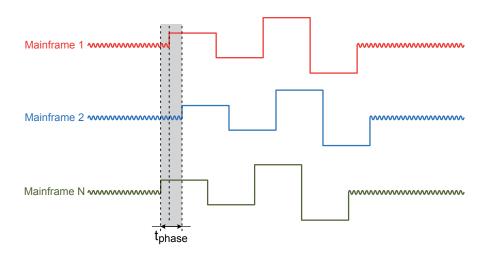

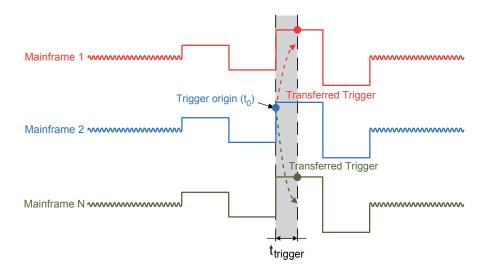

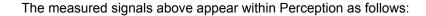

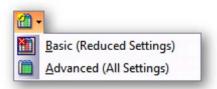

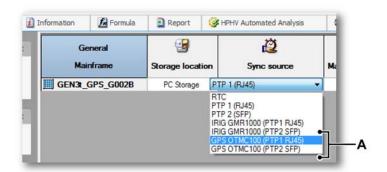

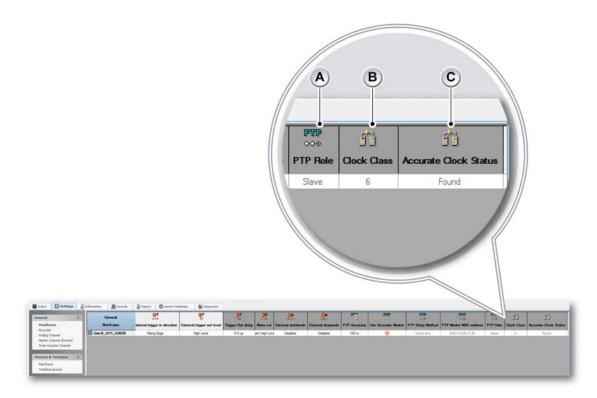

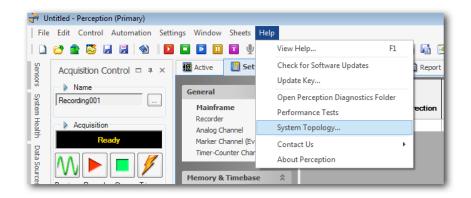

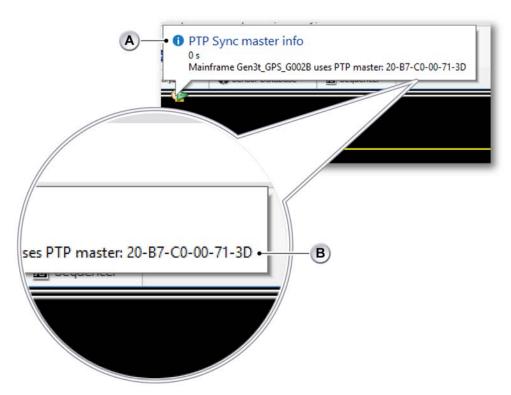

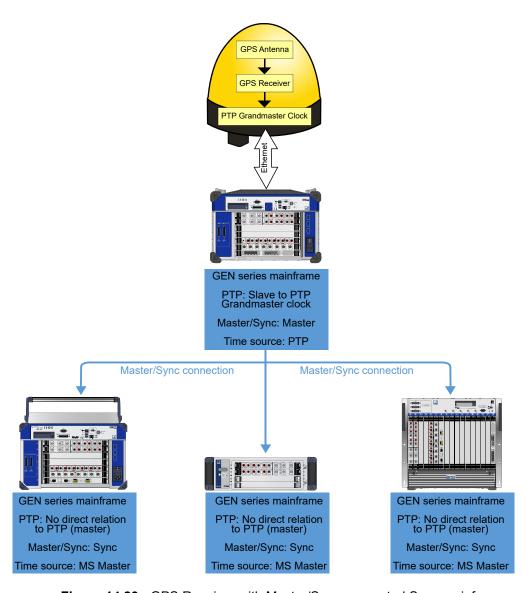

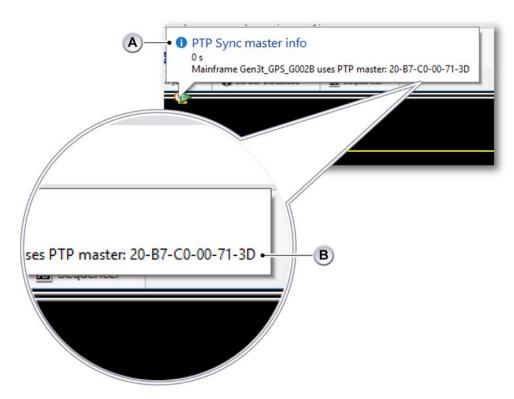

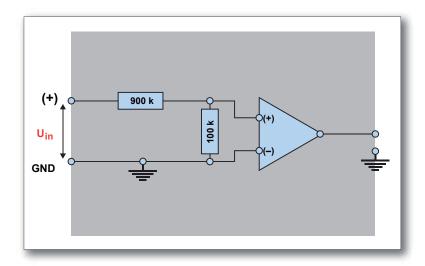

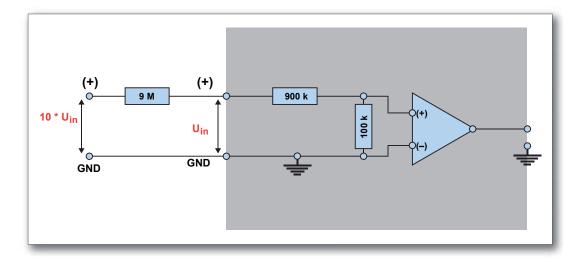

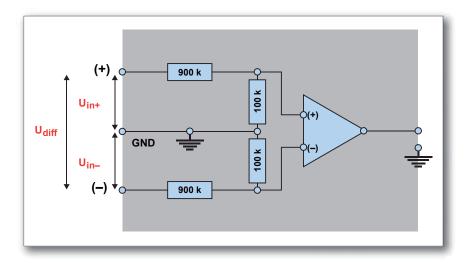

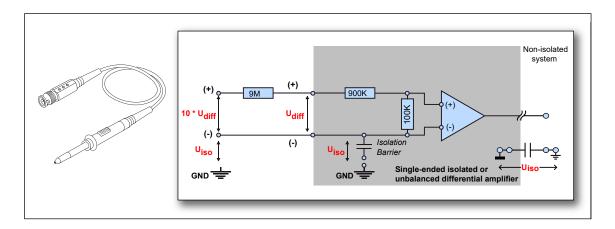

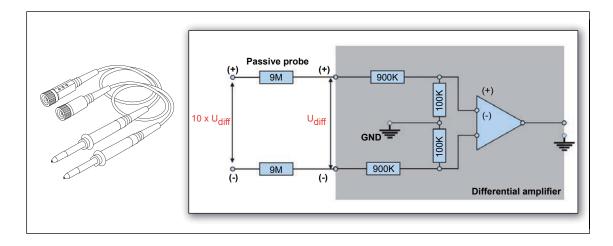

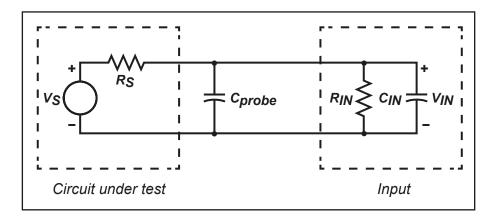

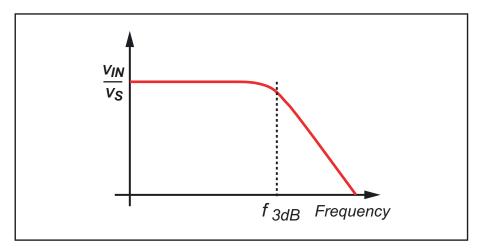

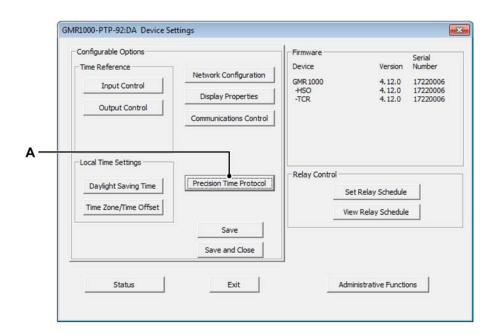

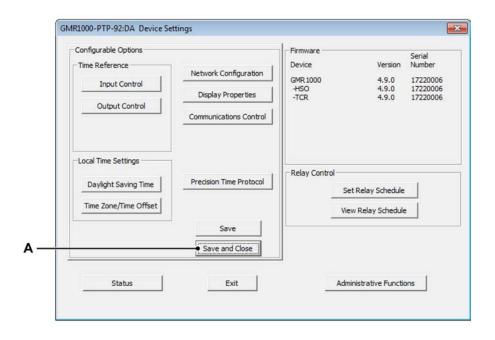

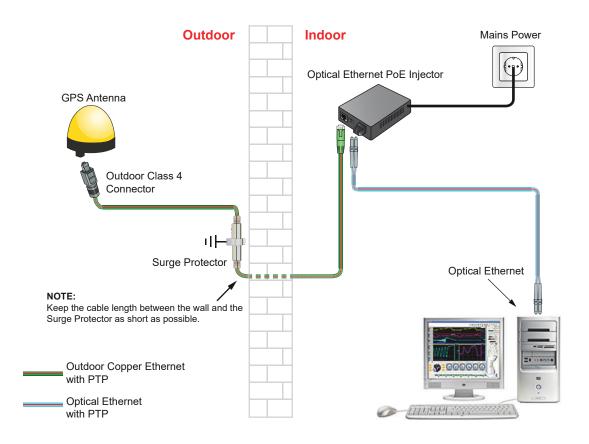

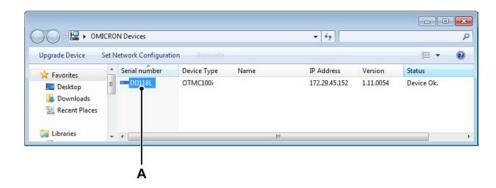

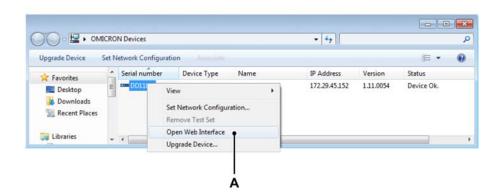

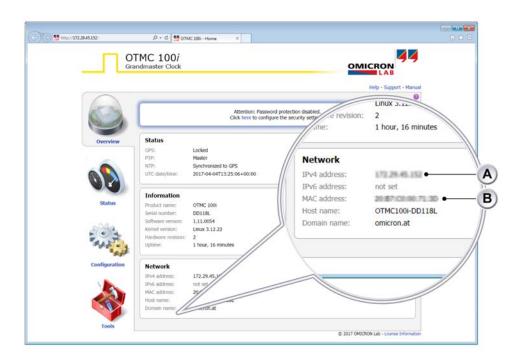

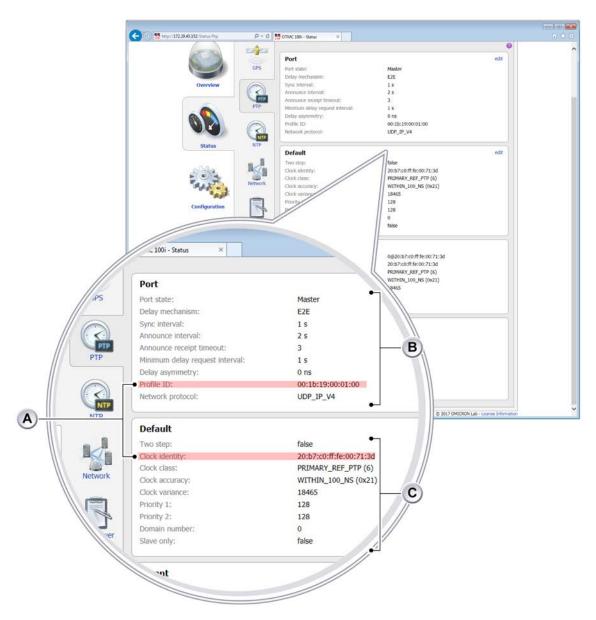

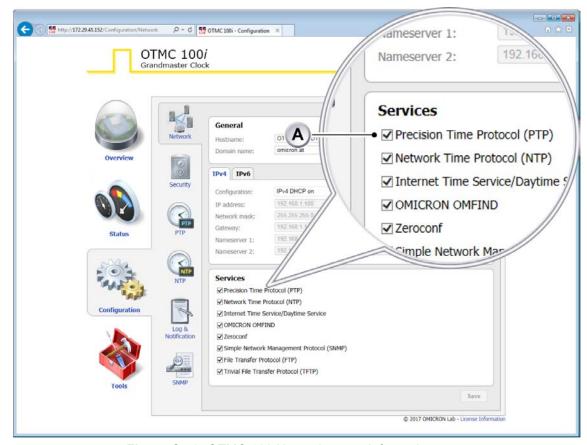

Dra ut IEC-kontakten för att koppla loss instrumentet eller dess strömkälla från strömförsörjningen. Brytaren för växelströmförsörjningen på detta instrument är endast avsedd för funktionella syften. Den är inte avsedd eller lämplig som frånkopplingsenhet.