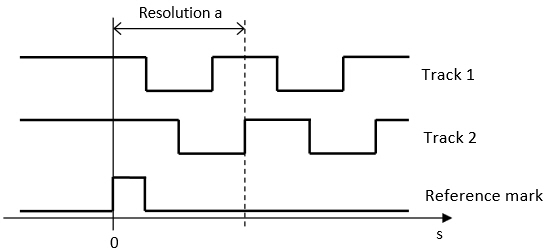

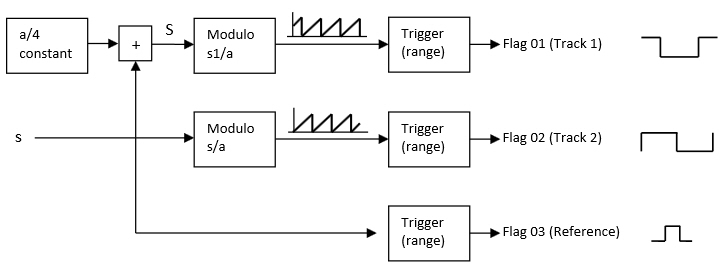

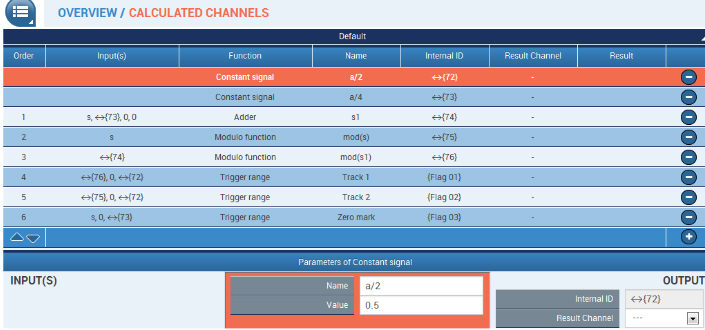

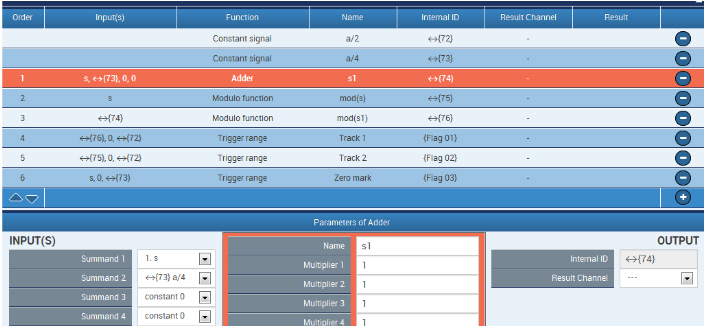

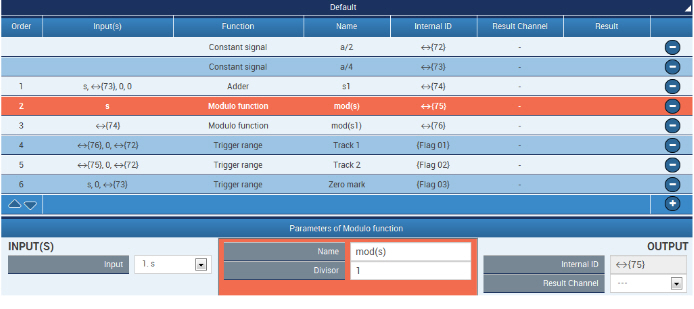

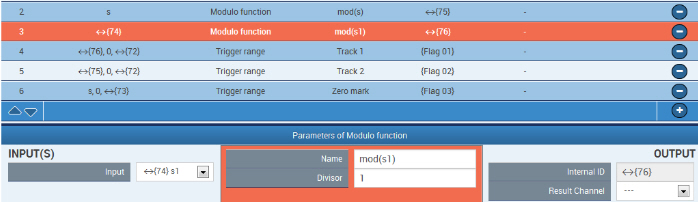

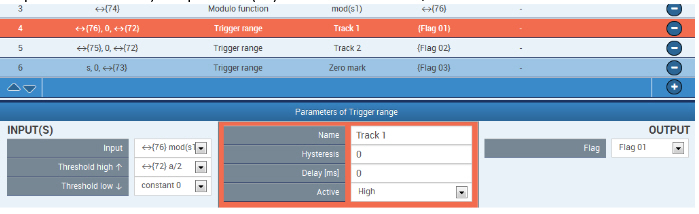

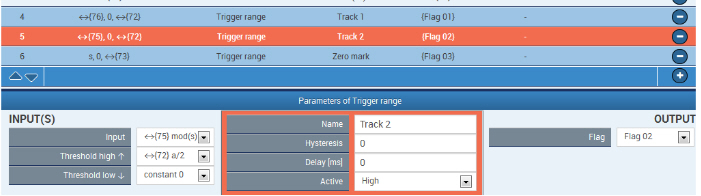

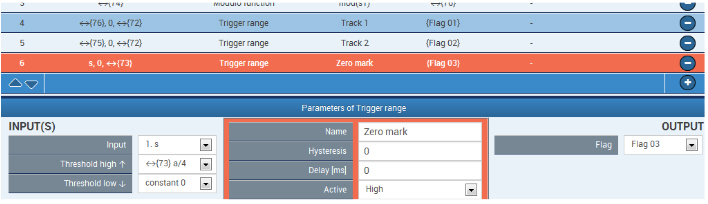

I seguenti segnali digitali vengono derivati dal segnale s:

Ad esempio, s è lo spostamento in mm od un angolo in gradi. La risoluzione è esattamente un periodo del segnale di uscita ed ha la stessa unità del segnale s.

Il metodo utilizzato non supporta i valori s negativi.

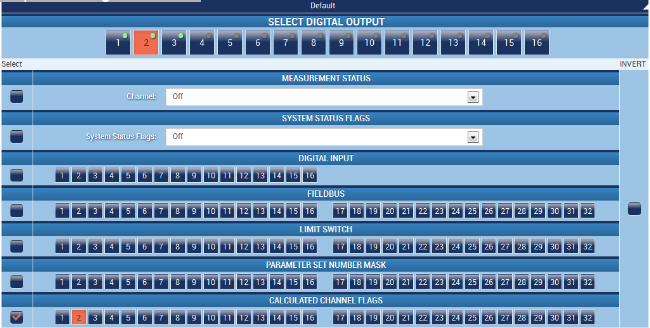

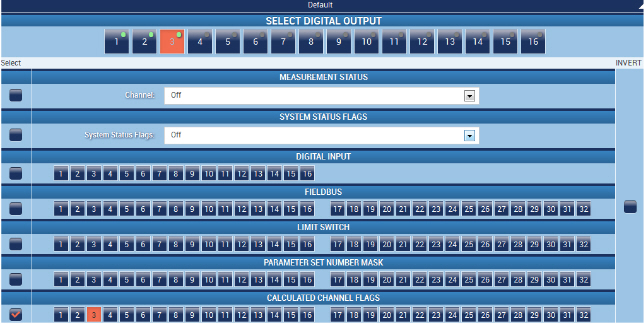

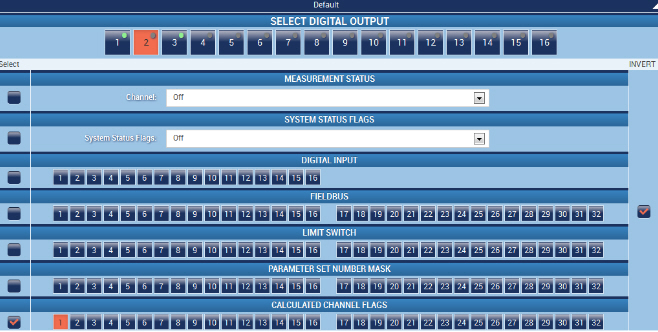

I segnali vengono inviati alle uscite digitali di una scheda-inserto PX878. La proprietà elettrica massima banda passante di frequenze è di circa 1 kHz.